OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

11) Número de publicación: 2 992 672

21) Número de solicitud: 202330494

(51) Int. Cl.:

H01L 21/36 (2006.01) H10D 62/83 (2015.01)

(12)

### PATENTE DE INVENCIÓN CON EXAMEN

B2

(22) Fecha de presentación:

13.06.2023

(43) Fecha de publicación de la solicitud:

16.12.2024

Fecha de concesión:

23.10.2025

(45) Fecha de publicación de la concesión:

30.10.2025

(73) Titular/es:

UNIVERSIDAD DE CÁDIZ (100.00%) Paseo Carlos III, nº 9 11007 Cádiz (Cádiz) ES

(72) Inventor/es:

ARAUJO GAY, Daniel; CAÑAS FERNÁNDEZ, Jesús; LLORET VIEIRA, Fernando Manuel y VILLAR CASTRO, María Del Pilar

(54) Título: TRANSISTOR DE EFECTO CAMPO DE UNIÓN DE DIAMANTE INTERDIGITADO (INTERJFET) Y PROCEDIMIENTO DE FABRICACIÓN

(57) Resumen:

La presente invención consiste en un transistor de efecto campo de unión (JFET) para electrónica de alta potencia mediante el crecimiento lateral/selectivo de diamante, basado en una geometría interdigitada, InterJFET.

Se trata de un enfoque original, un FET (transistor de efecto de campo) en depleción orientado verticalmente e interdigitado, InterJFET.

El método de fabricación incluye soluciones originales de crecimiento de diamantes, como el crecimiento selectivo y lateral. Este dispositivo permite corrientes de drenaje altas (de 16-32A a 10V de polarización en sustratos de 4x4 mm²) gracias a su arquitectura interdigitada que maximiza la "densidad de canales por superficie de sustrato". Esta arquitectura, además, puede trabajar a tensiones de hasta 3kV y a temperaturas superiores a 250°C.

Fia. 6

Aviso: Se puede realizar consulta prevista por el art. 41 LP 24/2015. Dentro de los seis meses siguientes a la publicación de la concesión en el Boletín Oficial de la Propiedad Industrial cualquier persona podrá oponerse a la concesión. La oposición deberá dirigirse a la OEPM en escrito motivado y previo pago de la tasa correspondiente (art. 43 LP 24/2015).

### **DESCRIPCIÓN**

TRANSISTOR DE EFECTO CAMPO DE UNIÓN DE DIAMANTE INTERDIGITADO (INTERJFET) Y PROCEDIMIENTO DE FABRICACIÓN

5

15

20

25

30

35

### **SECTOR DE LA TÉCNICA**

Sector industrial: Energía.

### 10 ANTECEDENTES DE LA INVENCIÓN

En un contexto generalizado de preocupación por el conflicto entre energía y medio ambiente, se espera un aumento extraordinario del uso de la electricidad en la producción, el transporte y el consumo de energía. Los nuevos sistemas de conversión de energía de electrónica de potencia (PE, por sus siglas en inglés) permitirán enormes ahorros energéticos y grandes mejoras en la calidad de vida. Todos los dispositivos que consumen energía, desde marcapasos y electrodomésticos hasta vehículos eléctricos y plantas de procesamiento de desechos industriales, se verán afectados. Todas las fuentes de energía alternativa, sostenible y distribuida, así como los sistemas de almacenamiento de energía, estarán vinculados a una red inteligente a través de convertidores de PE rápidos y eficientes.

En aplicaciones donde la sociedad exige una conversión de energía eléctrica cada vez mayor y más optimizada (energía renovable baja en carbono, energía de transporte y redes inteligentes) el impacto de la electrónica de potencia es sorprendente. Aproximadamente el 30% de toda la energía eléctrica generada utiliza PE en algún momento entre el punto de generación y su uso final. La PE se utiliza para un transporte, producción y distribución de energía renovable más eficiente, incluida la distribución de electricidad a largas distancias a través de líneas eléctricas de corriente continua de alto voltaje (HVDC), así como para un mejor control de las cargas en fuentes de alimentación conmutadas y de accionadores de velocidad variable en motores de ventiladores, bombas y compresores. Para 2030, se espera que hasta el 80% de toda la energía eléctrica utilice electrónica de potencia en algún punto entre su generación y su consumo. Sin embargo, con el estado actual de los equipos eléctricos, la transformación de la energía eléctrica conlleva importantes pérdidas (por

5

10

15

20

25

30

35

ejemplo un 9% en España desde la fuente hasta el punto de uso). Esto es debido a que los semiconductores disponibles no son los ideales para estas altas potencias.

El silicio es un material semiconductor bien establecido que ha abordado los requisitos de conversión de energía durante más de 50 años. Sin embargo, es ampliamente conocido (como puede verse en Research roadmaps on power semiconductor devices [1]) que el uso de dispositivos basados en materiales semiconductores de banda prohibida ancha (WBG, por sus siglas en inglés) resultaría en una mejora real en la electrónica de potencia. Estos materiales tienen características eléctricas muy superiores a las del silicio para aplicaciones en dispositivos de potencia. Muchas aplicaciones de red, por ejemplo para la red HVDC de 320 kV, utilizan convertidores multinivel, con semiconductores de potencia de silicio de 3,3 kV (y 6,5 kV) en serie para cada nivel de voltaje requerido. Para alcanzar una corriente de alto nivel, se requiere la conexión en paralelo de los dispositivos. Los dispositivos electrónicos de potencia basados en WBG darán lugar a mejoras sustanciales en el rendimiento de los sistemas electrónicos de potencia al ofrecer voltajes de bloqueo más altos, y mejores eficiencia y confiabilidad (mayor relación rendimiento/costo), además de conexión en paralelo más fácil, así como requisitos térmicos menores, lo que permite sistemas electrónicos más eficientes y ecológicos. Desde hace una década, empresas como ABB, Mitsubishi o Toshiba están utilizando Si IGBT o SiC MOSFET (por ejemplo Infineon, MOS: metal-oxide-semiconductor FET). Estos sistemas alcanzan en la actualidad los 6,5kV y el siguiente paso es que se llegue a 13kV para convertidores HVDC. En este punto, el diamante puede ser el único material capaz de alcanzar tal resistencia a la tensión, como se muestra en la Tabla 1. Además de su alta resistencia a la tensión, el diamante también es altamente tolerante contra la "alta densidad de potencia", lo que es muy deseable para dispositivos de ultra alta potencia.

**Tabla 1:** Las propiedades del diamante son sorprendentemente superiores a las de otros semiconductores cuando se considera su uso en dispositivos electrónicos de potencia. La figura de mérito de Johnson (FoM por sus siglas en inglés) es una medida del rendimiento final del dispositivo electrónico a alta potencia y alta frecuencia de un transistor, la FoM de Keyes mide el rendimiento limitado por la generación y eliminación de calor, y la FoM de Baliga mide el rendimiento limitado por pérdidas en Operación de alta potencia y alta frecuencia. Las propiedades/cifras en las que el diamante destaca para la presente invención están resaltadas en rojo.

| Propiedad (unidad)                                   | Si   | SiC-4H | GaN  | Ga <sub>2</sub> O <sub>3</sub> | Diamond |

|------------------------------------------------------|------|--------|------|--------------------------------|---------|

| Ancho de banda prohibida (eV)                        | 1.1  | 3.23   | 3.42 | 4.8                            | 5.45    |

| Constante dielectrica, ε                             | 11.8 | 9.7    | 9    | 10                             | 5,7     |

| Campo de ruptura (MV/cm)                             | 0.3  | 3      | 2    | 8                              | 10      |

| Movilidad de electrones (cm²/Vs)                     | 1500 | 1000   | 2000 | 300                            | 1000    |

| Movilidad de huecos (cm²/Vs)                         | 480  | 100    | 20   |                                | 2000    |

| Conductividad térmica (W/cmK)                        | 1.5  | 5      | 1.5  | 0.27                           | 22      |

| FoM de Johnson (10 <sup>23</sup> ΩW/s <sup>2</sup> ) | 2.3  | 900    | 490  | 1236                           | 2530    |

| FoM de Keyes (10 <sup>7</sup> W/Ks)                  | 10   | 53     | 17   | 2                              | 218     |

| FoM de Baliga (Normalizada al Si)                    | 1    | 554    | 188  | 3214                           | 23068   |

Debido a sus propiedades excepcionales [2], el diamante es considerado de entre todos los semiconductores WBG el semiconductor definitivo para aplicaciones en electrónica de alta potencia. Su resistencia a la ruptura dieléctrica es 3 veces superior a la del carburo de silicio (SiC) y más de 30 veces superior a la del silicio (Si). Además, a diferencia de la mayoría de los otros semiconductores WBG, la movilidad de ambos tipos de portadores es muy alta y su conductividad térmica es insuperable (véase la Tabla 1). Ello empuja a su utilización en la industria donde, en 1995, se patentó un FET de diamante que usa una arquitectura en forma de mesa [3]. El transistor hace uso de un sustrato sobre el que se crece diamante heteroepitaxialmente. A pesar de que se dice que el dispositivo puede ser con diamante mono o policristalino, en la actualidad no es posible crecer diamante monocristalino sobre sustratos que no sean a su vez diamante monocristalino. Esto es debido a que pequeñas diferencias de parámetro de red entre el sustrato y la capa de diamante resultan en una altísima densidad de defectos. Por otra parte, las fronteras de grano del diamante policristalino tienen un alto contenido de grafito y actúan como caminos eléctricos cortocircuitando el dispositivo.

5

10

15

20

25

Tres décadas más tarde se patentó un MOSFET de estructura tridimensional cuyo proceso de fabricación permite que sea todo él de diamante monocristalino [4]. Este diseño contempla la posible existencia de defectos cristalinos, resolviéndose de esta forma uno de los principales problemas que presentan estos dispositivos. Si bien, no tiene en cuenta otros problemas tecnológicos igualmente importantes. En MOSFET de diamante, hasta la fecha, la inversión se ha demostrado solo muy recientemente en la superficie del diamante orientado (111) [4], mientras que la acumulación se ha obtenido con la superficie del diamante terminada en oxígeno cuando se deposita SiO<sub>2</sub>.

El problema principal es la configuración de óxido/diamante donde los estados de interfaz pueden fijar el nivel de Fermi y evitar la formación de un gas 2D de portadores (2DG) debido a una configuración de banda inadecuada en la intercara. Este problema no es sencillo, el tipo de crecimiento (3D o 2D), la mala orientación de corte del sustrato (*miscut*), así como muchos otros aspectos pueden cambiar los enlaces "libres" en la interfaz y modificar la fijación del nivel de Fermi (*Fermi level pinning*). Por lo tanto, el control de estructuras de diamante/óxidos capaces de generar 2DG no es hoy factible y, por ello, un MOSFET de diamante no puede en la actualidad cumplir los requisitos que necesita la sociedad.

10

15

5

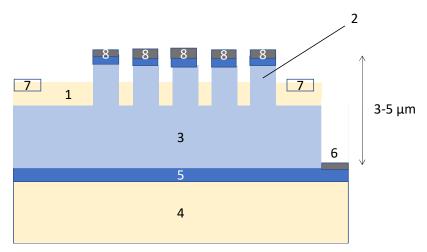

En consecuencia, esta invención presenta un enfoque alternativo, mucho más resolutivo. La figura 1 describe la estructura de la invención, que está basada en distintos pasos tecnológicos para su fabricación: (i) crecimiento de diamantes tipo p [6], (ii) crecimiento de diamantes tipo n [7], (iii) crecimiento lateral o crecimiento selectivo [8], (iv) fabricación de contactos [9] y grabado ICP del diamante [10], (v) caracterización eléctrica [11], (vi) caracterización estructural [12], (vii) evaluación de dopaje [13], banda prohibida [14] y ajuste de banda [15]. Además, se requiere un control de los parámetros de crecimiento como el nivel de dopaje, el corte incorrecto, etc. para lograr capas de diamante homoepitaxial de buena calidad [16].

20

25

30

35

### **DESCRIPCIÓN DE LA INVENCIÓN**

En este contexto, la presente invención consiste en un dispositivo transistor basado en diamante y su método de fabricación. Se trate de un enfoque original, un FET (transistor de efecto de campo) en depleción orientado verticalmente e interdigitado, InterJFET. El método de fabricación incluye soluciones originales de crecimiento de diamantes, como el crecimiento selectivo y lateral. Este dispositivo permite corrientes de drenaje altas (de 16-32A a 10V de polarización en sustratos de 4x4 mm²) gracias a su arquitectura interdigitada que maximiza la "densidad de canales por superficie de sustrato". Esta arquitectura, además, puede trabajar a tensiones de hasta 3kV y a temperaturas superiores a 250°C.

La invención utiliza una arquitectura vertical que permite aumentar la densidad de corriente de drenaje y la tensión de ruptura dieléctrica frente a dispositivos laterales [17]. Se trata de un dispositivo novedoso al ser un transistor vertical de diamante con

conducción bulk o en masa. Para conducción superficial y arquitectura vertical (que permite aumentar la corriente total) solo se conoce un ejemplo de un MOSFET de diamante [18][19], en este caso funciona en modo inversión, 2DG. Además, la unión p-n de la invención hace posible el estado "Normally OFF" del JFET, mientras que estos últimos reportados en la bibliografía son "Normally ON" lo cual hace que no sean estables debido al concepto de terminación H (fluctuaciones de corriente en modo ON). Como se ha dicho, para obtener un estado "Normally OFF", se utiliza una unión p-n para cerrar el canal vertical. No sería posible técnicamente utilizar una unión Schottky ya que deposiciones metálicas en superficies verticales no son técnicamente posibles. El problema de la deposición vertical entre los dígitos se resuelve mediante el crecimiento por MPCVD (deposición química de vapor asistida por plasma de microondas) de una capa dopada n que genera una zona depletada. En efecto, el crecimiento de diamante MPCVD de una capa de tipo n puede hacerse fácilmente de dos maneras: (i) mediante un paso de crecimiento selectivo o (ii) mediante crecimiento lateral. Esta capa permite por una parte incrementar la corriente en el estado ON y por otra parte incrementar la resistencia a la tensión (una unión p-n es más resistente que un contacto Schottky) permitiendo trabajar a mayores potencias. El ajuste de los niveles de dopados es fundamental para dimensionar correctamente la zona depletada y la zona de deriva evitando si fuera posible el punch-through. El diseño de la propuesta (figuras 1 y 2) permite una tensión superior a 1kV.

Por otra parte, para lograr una densidad de interfaces verticales muy alta, es decir, para maximizar la corriente total por superficie de sustrato, la propuesta presenta un concepto interdigitado, solo posible gracias a su arquitectura vertical. De esta forma permite llegar a corrientes de 30-100A por sustrato de 4mm x 4mm. La resistencia normalizada para cada dispositivo es de 3 m $\Omega$  cm $^2$ . Este valor es similar a los mejores valores obtenidos para FET verticales terminados en H.

#### BREVE DESCRIPCIÓN DE LOS DIBUJOS

30

35

5

10

15

20

25

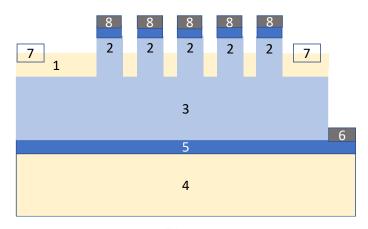

**Figura 1:** Descripción esquemática en vista transversal del InterJFET de la invención. Sobre el sustrato (4) se crece una capa dopada p<sup>+</sup> (5) en la cual se fabricará el contacto óhmico de drenador (6). El crecimiento de MPCVD, al ser selectivo, permitirá hacer crecer las regiones dopadas p del dispositivo (3), así como las regiones dopadas n (1). Sobre estos se fabricará los contactos de fuente (8) y puerta (7) respectivamente. Se

consideran alternativas al crecimiento selectivo (ver sección "Modo de realización de la invención"). El estado *Normally OFF* se logra gracias a la zona depletada de la unión p-n. Se puede apreciar que las dimensiones críticas como la profundidad y ancho de los interdigitos hacen difícil una fotolitografía láser. Por ello se debe utilizar electrolitografía y/o nanomecanizado FIB.

5

10

20

25

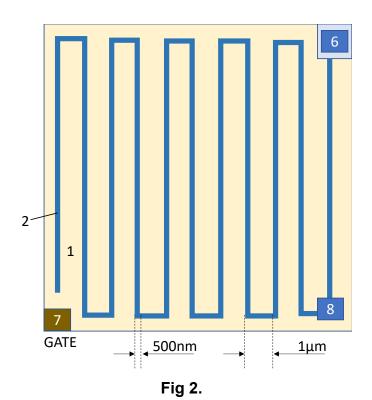

- **Figura 2:** Descripción esquemática desde arriba (vista superior) de todo el sustrato revelando la estructura interdigitada. Se han marcado los contactos de drenador (6) fuente (8) y puerta (7). Este último cierra lateralmente el canal por ambos lados (1) con un canal vertical dopado p (2). No se respetan las dimensiones y tamaños relativos (ver por ejemplo los tamaños entre dígitos).

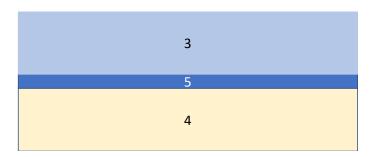

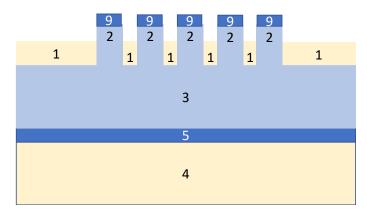

- **Figura 3:** Proceso primero de fabricación del dispositivo. Crecimiento sobre el sustrato (4) de la bicapa formada por una capa altamente dopada tipo p, p<sup>+</sup> (5), seguida de una capa con bajo dopado tipo p, p<sup>-</sup> (3).

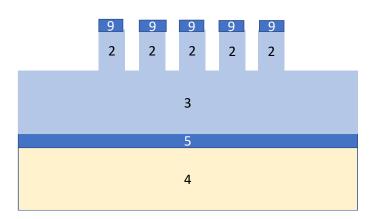

- **Figura 4:** Proceso de fabricación de la estructura interdigitada (2) formada por una capa primera con bajo dopado tipo p, p<sup>-</sup>, (3) seguida de una capa altamente dopada tipo p, p<sup>+</sup> (9). La fabricación de esta estructura puede realizarse mediante dos procesos alternativos:

- Opción A: Crecimiento selectivo, usando una máscara de Ti, de una estructura p-/p+ (2 y 9) sobre la primera bicapa p+/p- (5 y 3).

- Opción B: Crecimiento de una capa p+ (9) sobre la bicapa p+/p- (5 y 3) previamente crecida y nanomecanizado posterior con microscopio de haz de iones focalizados (FIB por sus siglas en inglés), o mediante ataque con plasma acoplado inductivamente (ICP por sus siglas en inglés) y electrolitografía, sobre las capas p-/p+ para la generación de las "columnas" (2 y 9, los interdigitos).

- Figura 5: Proceso de fabricación de la capa tipo n (1). Mediante crecimiento selectivo (con máscara de Ti y electrolitógrafía antes del crecimiento) se crece una capa de diamante tipo n

- **Figura 6:** Fabricación de los contactos. Sobre la estructura se fabrican los contactos de drenaje (6), fuente (8) y puerta (7). El contacto de puerta se fabrica directamente sobre la capa dopada tipo n (1). El contacto de fuente se debe fabricar sobre los

interdígitos (2). Por último, para la fabricación del contacto de drenador se debe grabar la estructura por uno de sus extremos hasta contactar la primera de las capas dopadas tipo p<sup>+</sup> crecida (5). El proceso de fabricación de los contactos se puede llevar a cabo mediante electrolitografía y PVD, ICP o FIB.

5

10

### REALIZACIÓN PREFERENTE DE LA INVENCIÓN

La invención consiste en un transistor de efecto campo de unión (JFET) para electrónica de alta potencia obtenido mediante el crecimiento lateral/selectivo de diamante, basado en una geometría interdigitada.

El JFET objeto de la invención comprende:

- a) Un sustrato de diamante de calidad electrónica y convenientemente pulido (rugosidad superficial ≤1 nm).

- b) Una primera capa de material diamante semiconductor altamente dopado tipo p+.

- c) Una segunda capa de material diamante de bajo dopado tipo p-.

- d) Una tercera capa de diamante bajo dopado tipo p- consistente en una estructura digitada.

- e) Una cuarta capa de diamante altamente dopado tipo p+ que continúa verticalmente la estructura digitada anterior.

- f) Una quinta capa de material diamante semiconductor dopado tipo n crecido sobre las laderas de cada estructura digitadas de la capa anterior.

- g) Grabados en sus extremos, de profundidad suficiente para que lleguen hasta la primera capa de diamante semiconductor tipo p+.

25

20

Algunas características del JFET son las siguientes:

- Hace uso de diamante monocristalino como sustrato y material activo.

- La segunda capa de diamante p<sup>-</sup> presenta un grabado en su superficie de forma que exhibe una estructura interdigitada.

- La primera capa, de diamante semiconductor p⁺, tiene una concentración de boro comprendida en el rango 10¹¹√<[B]<10²⁴ cm⁻³.</li>

- Su segunda y tercera capa, de diamante p<sup>-</sup>, tienen una concentración de boro comprendida en el rango 10<sup>15</sup><[B]<10<sup>17</sup>cm<sup>-3</sup>.

- Su cuarta capa, de diamante semiconductor p<sup>+</sup>, tiene una concentración de boro comprendida en el rango 10<sup>17</sup><[B]<10<sup>24</sup> cm<sup>-3</sup>

- Su capa quinta, de diamante dopado tipo n, está depositada en el espaciado entre los dígitos de material diamante p<sup>-</sup>/p+.

Sus contactos de drenador están fabricados sobre la primera capa diamante tipo  $p^+$ , los contactos de fuente están fabricados sobre los dígitos de la última capa diamante tipo  $p^+$  y los contactos de puerta están fabricados sobre la capa de diamante tipo n, pero en ninguno de los casos tienen que limitarse a ocupar esas capas.

A continuación, se describe un modo de realización preferente del objeto de la invención desarrollada.

10

15

5

Sobre un sustrato de diamante comercial de alta calidad y baja rugosidad (calidad electrónica y finamente pulida) se crecerá una capa de alto dopado tipo p (capa p<sup>+</sup>). Esto se logra mediante el dopado del diamante con boro. Sobre esta capa altamente dopada, que actuará como contacto de drenaje, se crece otra capa con bajo dopado (capa p<sup>-</sup>) que actuará como capa de deriva. El contacto de drenaje necesita un nivel de dopaje B de 10<sup>19</sup>-10<sup>20</sup> cm<sup>-3</sup>, para tener un carácter óhmico con una baja resistencia de contacto, mientras que la capa de deriva que se crece sobre ella necesita niveles de dopaje de alrededor de 1-3 x 10<sup>16</sup> cm<sup>-3</sup>. Por lo tanto, el crecimiento debe realizarse en reactores distintos o cambiando el tubo de cuarzo de la cámara MPCVD entre los crecimientos de ambas capas.

20

Para la fabricación de los interdigitos se proponen dos opciones igualmente válidas: Opción A: Crecimiento selectivo, usando una máscara de Ti, de una estructura  $p^-/p^+$  sobre la primera bicapa  $p^+/p^-$ .

25

Opción B: Crecimiento de una capa p<sup>+</sup> sobre la bicapa p<sup>+</sup>/p<sup>-</sup> previamente crecida y nanomecanizado posterior con microscopio de haz de iones focalizados (FIB por sus siglas en inglés), o mediante ataque con plasma acoplado inductivamente (ICP por sus siglas en inglés) y electrolitografía, sobre las capas p<sup>-</sup>/p<sup>+</sup> para la generación de las "columnas" (los interdigitos).

30

35

Una vez fabricados los interdígitos de cualquiera de las opciones propuestas, se crece selectivamente una capa dopada tipo n, que puede ser dopada con nitrógeno o con fósforo (con máscara de Ti y electrolitografía antes del crecimiento). Esta capa genera un SCR que cerrará el canal para el estado *Normally-OFF*. Debido a que el dopado debe ser tipo n, este crecimiento debe realizarse en un reactor diferente al empleado

para el dopado con boro, de forma que se garantice que no haya contaminación cruzada.

Sobre esta estructura se fabrican los contactos de drenaje, fuente y puerta. El contacto de puerta se fabrica directamente sobre la capa dopada tipo n. El contacto de fuente se debe fabricar sobre los interdígitos. Por último, para la fabricación del contacto de drenador se debe grabar la estructura por uno de sus extremos hasta contactar la primera de las capas dopadas tipo p<sup>+</sup> crecida. El proceso de fabricación de los contactos se puede llevar a cabo mediante electrolitografía y PVD, ICP o FIB.

10

5

Debe hacerse notar que, debido al requisito de tener espaciados muy estrechos (para alcanzar el estado *Normally OFF* con dopados p de 2 x  $10^{16}$  cm<sup>-3</sup> se requiere un espacio entre dígitos de 2-3  $\mu$ m) es necesario el uso de electrolitografía que proporcione una precisión en el rango del nm.

15

20

#### Referencias

- [1] H. Ohashi, Proceedings of the 24th ISPSD 3-7 June 2012, Bruges, Belgium.

- [2] D. Araujo, M. Suzuki, F. Lloret, G. Alba and P. Villar, Diamond for Electronics: Materials, Processing and Devices, Materials 14, 7081 (2021). https://doi.org/10.3390/ma14227081.

- [3] D. L. Dreifus, patente JPH06177400A, Kobe Steel LTD, 1994

- [4] F. Lloret, D. Araujo, P. Godignon, D. Eon, J. Pernot, E. Bustarret, Patente ES2763702A1, Universidad de Cádiz, CSIC, 2020.

- [5] T. Matsumoto, H. Kato, T. Makino, M. Ogura, D. Takeuchi, S. Yamasaki, T. Inokuma and N. Tokuda, Inversion channel mobility and interface state density of diamond MOSFET using N-type body with various phosphorus concentrations, Appl. Phys. Lett. 114, 242101 (2019).

- [6] F. Lloret, A. Fiori, D. Araujo, D. Eon, M. P. Villar, and E. Bustarret, Stratigraphy of a diamond epitaxial three-dimensional overgrowth using doping superlattices, Appl.

- 30 Phys. Lett. 108, 181901 (2016) // R. Rouzbahani, Sh. S. Nicley, D. E.P. Vanpoucke, F. Lloret, P. Pobedinskas, D. Araujo, K. Haenen, Impact of methane concentration on surface morphology and boron incorporation of heavily boron-doped single crystal diamond layers, Carbon 172, 463 (2021)

- [7] S. Koizumi, M. Suzuki, n-type doping of diamond, Phys. Stat. Sol. A 203, 3358

(2006) // F. Lloret, B. Soto, R. Rouzbahani, M. Gutierrez, K. Haenen, D. Araujo, "High phosphorous incorporation in (100)-oriented MP CVD diamond growth", Diamond &

- Related Materials 133, 109746 (2023)

- [8] F. Lloret, D. Eon, E. Bustarret, F. Donatini, and D. Araujo, Selectively boron doped homoepitaxial diamond growth for power device applications, Appl. Phys. Lett. 118, 023504 (2021); https://doi.org/10.1063/5.0031478.

- [9] G. Alba, D. Leinen, M.P. Villar, R. Alcántara, J.C. Piñero, A. Fiori, T. Teraji, D. Araujo, Comprehensive nanoscopic analysis of tungsten carbide/Oxygenated-diamond contacts for Schottky barrier diodes, Appl. Surf. Sci. 537, 147874 (2021), https://doi.org/10.1016/j.apsusc.2020.147874.

- [10] B. Soto, J. Cañas, M.P. Villar, D. Araujo and J. Pernot. Transport mechanism in O-terminated diamond/ZrO2 based MOSCAPs, Diam. Rel. Mater 121, 108745 (2021), https://doi.org/10.1016/j.diamond.2021.108745 //

- [11] T. T. Pham, J. C. Piñero, A. Maréchal, M. Gutiérrez, F. Lloret, D. Eon, E. Gheeraert, N. Rouger, D. Araújo and J. Pernot, Impact of Nonhomoepitaxial Defects in Depleted Diamond MOS Capacitors, IEEE Trans. On Electr. Dev. 65, 1830 (2018) // M. Suzuki,

- T. Sakai, T. Makino, H. Kato. D. Takeuchi, M. Ogura, H. Okushi and S. Yamasaki, "Electrical characteristics of 5 kV PiN diodes", Proceedings of Hasselt Diamond Workshop 2014, p.71. See also: M. Suzuki, "High voltage diamond pin diodes". Oyo Buturi 85, 218 (2016).

- [12] M. P. Alegre, D. Araújo, A. Fiori, J. C. Pinero, F. Lloret, M. P. Villar, P. Achatz, G.

- 20 Chicot, E. Bustarret, and F. Jomard, Critical boron-doping levels for generation of dislocations in synthetic diamond, Appl. Phys. Lett. 105, 173103 (2014); doi: 10.1063/1.4900741

- [13] D. Araujo, M.P. Alegre, A. García, P. Villar, E. Bustarret, Ph. Achatz, P.N. Volpe,F. Omnès, Phys. Stat. Sol. (c) 8, 1366 (2011) / DOI 10.1002/pssc.201083991 // D.

- 25 Araujo, M.P. Alegre, A. García, P. Villar, E. Bustarret, Ph. Achatz, P.N. Volpe, F. Omnès, Phys. Stat. Sol. (c) 8, 1366 (2011) / DOI 10.1002/pssc.201083991

- [14] J. Cañas, J.C. Piñero, F. Lloret, M. Gutierrez, T. Pham, J. Pernot, D. Araujo, Determination of alumina bandgap and dielectric functions of diamond MOS by STEM-VEELS, Appl. Surf. Sci. 461, 93 (2018)

- 30 [15] J. Cañas, G. Alba, D. Leinen, F. Lloret, M. Gutierrez, D. Eon, J. Pernot, E. Gheeraert, D. Araujo, Diamond/γ-alumina band offset determination by XPS, Appl. Sur. Sci. 535, 146301 (2021), https://doi.org/10.1016/j.apsusc.2020.146301

- [16] F. Lloret, D. Eon, E. Bustarret, A. Fiori and D. Araujo, Boron-Doping Proximity Effects on Dislocation Generation during Non-Planar MPCVD Homoepitaxial Diamond

- 35 Growth, Nanomaterials 8, 480 (2018); doi:10.3390/nano8070480 // D. Araujo, F. Lloret,

- G. Alba, M. P. Alegre, and M. P. Villar, Dislocation generation mechanisms in heavily boron-doped diamond epilayers, Appl. Phys. Lett. 118, 052108 (2021); https://doi.org/10.1063/5.0031476

- [17] J. Cañas et al, MRS Fall Meeting in Boston (November 30, 2021): "1kV Normally

OFF Diamond lateral reverse blocking MESFET"

- [18] M. Iwataki et al., "Over 12000 A/cm2 and 3.2 m□ cm2 Miniaturized Vertical-Type Two-Dimensional Hole Gas Diamond MOSFET," in IEEE Electron Device Letters, vol. 41, no. 1, pp. 111-114, Jan. 2020, doi: 10.1109/LED.2019.2953693

- [19] H. Kawarada et al., "Diamond MOSFETs using 2D hole gas with 1700V breakdown

voltage," 2016 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2016, pp. 483-486, doi: 10.1109/ISPSD.2016.7520883.

#### **REIVINDICACIONES**

- 1.- Transistor de efecto campo de unión (JFET) para electrónica de alta potencia mediante el crecimiento lateral/selectivo de diamante, basado en una geometría interdigitada.

- 2.- Transistor de efecto campo de unión (JFET) para electrónica de alta potencia mediante el crecimiento lateral/selectivo de diamante, según reivindicación 1, que comprende:

- a) Un sustrato de diamante de calidad electrónica y convenientemente pulido (rugosidad superficial ≤1 nm).

- b) Una primera capa de material diamante semiconductor altamente dopado tipo p+.

- c) Una segunda capa de material diamante de bajo dopado tipo p-.

5

15

25

30

- d) Una tercera capa de diamante bajo dopado tipo p- consistente en una estructura digitada.

- e) Una cuarta capa de diamante altamente dopado tipo p+ que continúa verticalmente la estructura digitada anterior.

- f) Una quinta capa de material diamante semiconductor dopado tipo n crecido sobre las laderas de cada estructura digitadas de la capa anterior.

- g) Grabados en sus extremos, de profundidad suficiente para que lleguen hasta la primera capa de diamante semiconductor tipo p+.

- 3.- Transistor de efecto campo de unión (JFET) para alta potencia mediante crecimiento lateral/selectivo de diamante, según reivindicación 1 y 2, que hace uso de diamante monocristalino como sustrato y material activo.

- 4.- Transistor de efecto campo de unión (JFET) de diamante para alta potencia mediante crecimiento lateral/selectivo, según reivindicaciones 1, 2 y 3, caracterizado porque la segunda capa de diamante p<sup>-</sup> presenta un grabado en su superficie de forma que exhibe una estructura interdigitada.

- 5.- Transistor de efecto campo de unión (JFET) de diamante para alta potencia mediante crecimiento lateral/selectivo, según reivindicaciones 1, 2, 3 y 4, cuya primera capa, de diamante semiconductor  $p^+$ , tiene una concentración de boro comprendida en el rango  $10^{17}$ <[B]< $10^{24}$  cm<sup>-3.</sup>

6.- Transistor de efecto campo de unión (JFET) de diamante para alta potencia mediante crecimiento lateral/selectivo, según reivindicaciones 1, 2, 3, 4 y 5, cuya segunda y tercera capa, de diamante p<sup>-</sup>, tiene una concentración de boro comprendida en el rango 10<sup>15</sup><[B]<10<sup>17</sup>cm<sup>-3</sup>.

5

10

15

- 7.- Transistor de efecto campo de unión (JFET) de diamante para alta potencia mediante crecimiento lateral/selectivo, según reivindicaciones 1, 2, 3, 4, 5 y 6, cuya cuarta capa, de diamante semiconductor p<sup>+</sup>, tiene una concentración de boro comprendida en el rango 10<sup>17</sup><[B]<10<sup>24</sup> cm<sup>-3</sup>

- 8.- Transistor de efecto campo de unión (JFET) de diamante para alta potencia mediante crecimiento lateral/selectivo, según reivindicaciones 1, 2, 3, 4, 5, 6 y 7, cuya capa quinta, de diamante dopado tipo n, está depositada en el espaciado entre los dígitos de material diamante p<sup>-</sup>/p+.

- 9.- Transistor de efecto campo de unión (JFET) de diamante para alta potencia mediante crecimiento lateral/selectivo, según reivindicaciones 1, 2, 3, 4, 5, 6, 7 y 8, cuyos contactos de drenador están fabricados sobre la primera capa diamante tipo p<sup>+</sup>, los contactos de fuente están fabricados sobre los dígitos de la última capa diamante tipo p<sup>+</sup> y los contactos de puerta están fabricados sobre la capa de diamante tipo n, pero en ninguno de los casos tienen que limitarse a ocupar esas capas.

- 10.- Procedimiento de fabricación de un transistor de efecto campo de unión (JFET)

25 de diamante, según reivindicaciones 1 a 9, que se realiza sobre un sustrato de diamante de calidad electrónica y convenientemente pulido, que comprende las siguientes etapas:

- a) Crecimiento de una primera capa de diamante dopado tipo p, p<sup>+</sup>.

- b) Crecimiento de una segunda capa de diamante no dopado tipo p, p<sup>-</sup>.

- 30 c) Crecimiento de una tercera capa de diamante dopado p, p<sup>+</sup>.

- d) Grabado de la segunda y tercera capa de diamante con estructuras digitadas.

- e) Crecimiento selectivo de una capa de diamante dopado tipo n entre las parades de las estructuras digitadas.

- f) Grabado en regiones fuera de la estructura tridimensional que alcancen la primera capa crecida p<sup>+</sup>.

- 11.- Procedimiento de fabricación de un transistor de efecto campo de unión (JFET) de diamante, según reivindicaciones 1 a 9, que se realiza sobre un sustrato de diamante de calidad electrónica y convenientemente pulido, que comprende las siguientes etapas:

- a) Crecimiento de una primera capa de diamante dopado tipo p, p<sup>+</sup>.

- b) Crecimiento de una segunda capa de diamante no dopado tipo p, p<sup>-</sup>.

- c) Crecimiento selectivo mediante máscara de una tercera capa de diamante dopado p, p-, formando una estructura digitada.

- d) Crecimiento selectivo mediante máscara de una cuarta capa de diamante dopado p, p<sup>+</sup>, sobre la capa anterior, continuando verticalmente la estructura digitada.

- e) Crecimiento selectivo de una capa de diamante dopado tipo n entre las parades de las estructuras digitadas.

- f) Grabado en regiones fuera de la estructura tridimensional que alcancen la primera

capa crecida p<sup>+</sup>.

- 12.- Procedimiento de fabricación de un transistor de efecto campo de unión (JFET), según reivindicación 10, en el que el crecimiento de la tercera capa, correspondiente a diamante dopado tipo n, se realiza lateralmente.

20

- 13.- Procedimiento de fabricación de un transistor de efecto campo de unión (JFET), según reivindicación 11, en el que el crecimiento de la tercera capa, correspondiente a diamante dopado tipo n, se realiza lateralmente.

- 25 14.- Procedimiento de fabricación de un transistor de efecto campo de unión (JFET), según reivindicación 10, en el que el crecimiento de la tercera capa, correspondiente a diamante dopado tipo n, se realiza selectivamente mediante máscara.

- 15.- Procedimiento de fabricación de un transistor de efecto campo de unión (JFET),

30 según reivindicación 11, en el que el crecimiento de la tercera capa, correspondiente a diamante dopado tipo n, se realiza selectivamente mediante máscara.

Fig.1

Fig. 3

Fig. 4

Fig. 5

Fig. 6