# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

**ESPAÑA**

(1) Número de publicación: 2819 191

51 Int. Cl.:

**H02M 7/515** (2007.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

Fecha de presentación y número de la solicitud europea: 09.08.2011 E 11176932 (9)

Fecha y número de publicación de la concesión europea: 01.07.2020 EP 2424101

(54) Título: Sistema inversor de potencia y método de puesta en marcha del mismo en un elevado voltaje de corriente continua

(30) Prioridad:

28.08.2010 US 870795

(45) Fecha de publicación y mención en BOPI de la traducción de la patente: 15.04.2021

(73) Titular/es:

GENERAL ELECTRIC COMPANY (100.0%) 1 River Road Schenectady, NY 12345, US

(72) Inventor/es:

EL-BARBARI, SAID FAROUK SAID y GALBRAITH, ANTHONY WILLIAM

(74) Agente/Representante:

**ELZABURU, S.L.P**

#### **DESCRIPCIÓN**

Sistema inversor de potencia y método de puesta en marcha del mismo en un elevado voltaje de corriente continua

- 5 Esta invención se refiere generalmente al campo de la generación de energía solar y, más concretamente, a métodos y sistemas para permitir un voltaje de fuente de corriente continua elevado en un sistema inversor de energía solar.

- La generación de energía solar se está convirtiendo en una fuente de energía progresivamente mayor en todo el mundo. En los sistemas de generación de energía solar típicamente incluyen uno o más matrices fotovoltaicas (matrices FV) que tienen múltiples celdas solares interconectadas que convierte la energía solar en energía eléctrica de corriente continua por medio del efecto fotovoltaico. Para interconectar la salida de las matrices FV a una red eléctrica pública, se utiliza un sistema convertidor de energía para cambiar la corriente continua y la salida de voltaje de corriente continua de la matriz FV a una onda de corriente alterna de 60/50 Hz que suministra energía a la red eléctrica pública.

- Existen diversos sistemas convertidores de energía para conectar la salida de corriente continua que una matriz FV (u otra fuente de alimentación de corriente continua) con la red de corriente alterna. Una implementación de un sistema convertidor de energía incluye dos etapas, una etapa de convertidor elevador y una etapa de inversor. La etapa de convertidor elevador controla el flujo de energía de corriente continua desde la matriz FV hasta un bus de corriente continua o un enlace de corriente continua (en lo que sigue denominado como "enlace de corriente continua). La etapa de inversor convierte la energía suministrada al enlace de corriente continua en una onda de corriente alterna adecuada que puede ser enviada a la red de corriente alterna.

20

60

65

- Surgen situaciones en las que es necesario adaptar una matriz FV (u otra fuente de alimentación de corriente continua) que tenga un voltaje de circuito abierto elevado, tal como un voltaje de circuito abierto que esté muy próximo a la tasa de voltaje de bloqueo de los dispositivos semiconductores empleados en el sistema inversor de potencia. Por ejemplo, el voltaje de circuito abierto de matriz es 1000 V de corriente continua y el voltaje de bloqueo de los dispositivos semiconductores es de 1200 V de corriente continua. Los dispositivos semiconductores inversores de potencia, tales como los transistores bipolares de puerta aislada (IGBTs), son típicamente seleccionados para adaptar el voltaje de potencia máximo de la matriz FV, no el voltaje de circuito abierto de la matriz FV. El factor limitante en la puesta en marcha a voltaje elevado es el exceso de voltaje en la desconexión de los IGBTs.

- La publicación de solicitud de patente US20100133904 describe un sistema de energía fotovoltaica que comprende un inversor, un circuito de enlace de corriente continua y un controlador.

- A la vista lo anterior, existe la necesidad de un sistema inversor energía solar y de un método de funcionamiento que permita un elevado voltaje de alimentación de corriente continua durante condiciones de puesta en marcha. El sistema inversor evitaría que el voltaje de enlace de corriente continua alcanzara o excediera el voltaje de bloqueo del dispositivo semiconductor del sistema inversor durante la puesta en marcha del inversor FV. La presente invención está definida en las reivindicaciones independientes.

- Una realización de la presente invención está dirigida a un sistema inversor de potencia, que comprende: un inversor de corriente continua a corriente alterna que comprende una pluralidad de dispositivos de conmutación semiconductores de potencia; un enlace de corriente continua que conecta la potencia de corriente continua de inversor, comprendiendo el enlace de corriente continua un condensador de enlace de corriente continua; y un controlador configurado para incrementar una resistencia de desconexión de puerta para cada uno de los dispositivos de conmutación semiconductores de potencia solo durante los periodos de puesta en marcha del sistema inversor, de manera que el voltaje de enlace de corriente continua no excede la tasa de voltaje de bloqueo del dispositivo de conmutación semiconductor durante los correspondientes periodos de desactivación de conmutación, en donde el periodo de puesta en marcha es el tiempo requerido para llevar un voltaje de fuente de alimentación de corriente continua correspondiente desde un voltaje de circuito abierto a un voltaje predeterminado que constituye una condición de funcionamiento segura para la pluralidad de dispositivos de conmutación semiconductores.

- Otra realización de la presente invención está dirigida a un método de funcionamiento de un sistema inversor de potencia, comprendiendo el método: proporcionar un inversor que comprende una pluralidad de dispositivos de conmutación semiconductores de potencia, un enlace de corriente continua que comprende un condensador, y un controlador de inversor; conectar una fuente de voltaje de corriente continua al inversor por medio del condensador de enlace de corriente continua; y después conectar la fuente de voltaje de corriente continua al inversor, incrementar una resistencia de desactivación de puerta para cada uno de los dispositivos de conmutación de potencia semiconductores solo durante sus correspondientes periodos de puesta en marcha, de manera que el voltaje de enlace de corriente continua no excede la respectiva tasa de voltaje de bloqueo de dispositivo de conmutación semiconductor de potencia durante los correspondientes periodos de desactivación de conmutación, en

donde el periodo de puesta en marcha es el tiempo requerido para llevar el voltaje de fuente de corriente continua desde un voltaje de circuito abierto hasta un voltaje predeterminado que constituye una condición de funcionamiento segura para la pluralidad de dispositivos de conmutación semiconductores de potencia.

- De acuerdo con todavía otra realización, un sistema inversor de potencia comprende una pluralidad de dispositivos de conmutación semiconductores de potencia, comprendiendo cada dispositivo de conmutación una resistencia de desactivación de puerta correspondiente configurada para aumentar durante los periodos de puesta en marcha del sistema inversor, de manera que el voltaje de circuito abierto de una correspondiente fuente de alimentación que proporciona energía al sistema inversor de potencia no excede las tasas de voltaje de bloqueo del dispositivo de conmutación durante los correspondientes periodos de desactivación de conmutación, en donde el periodo de puesta en marcha es el tiempo requerido para llevar el correspondiente voltaje de fuente alimentación desde su nivel de voltaje del circuito abierto hasta un voltaje predeterminado que constituye una condición de funcionamiento segura para la pluralidad de dispositivos de conmutación de semiconductor.

- Diversas características, aspectos, y ventajas de la presente invención se entenderán mejor cuando se lea la siguiente descripción detallada con referencia los dibujos adjuntos, en los que:

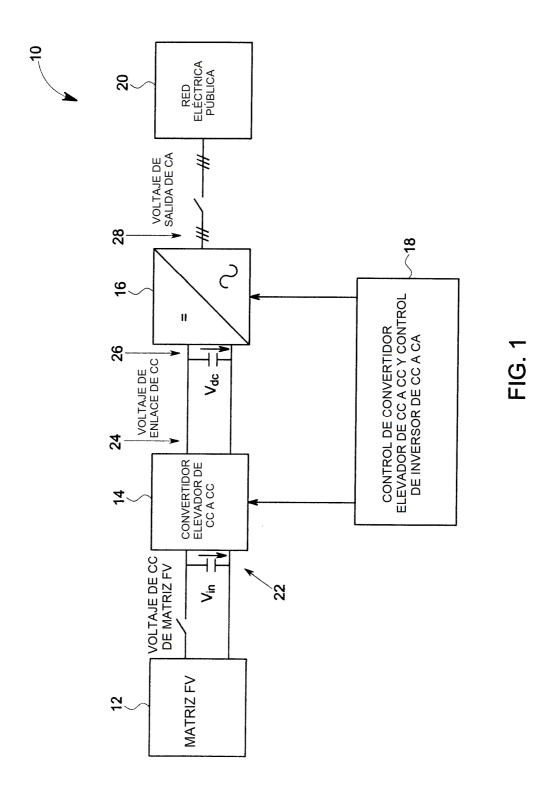

- La Figura 1 es un diagrama de bloques que ilustra un sistema inversor fotovoltaico de acuerdo con una realización a modo de ejemplo de la presente invención;

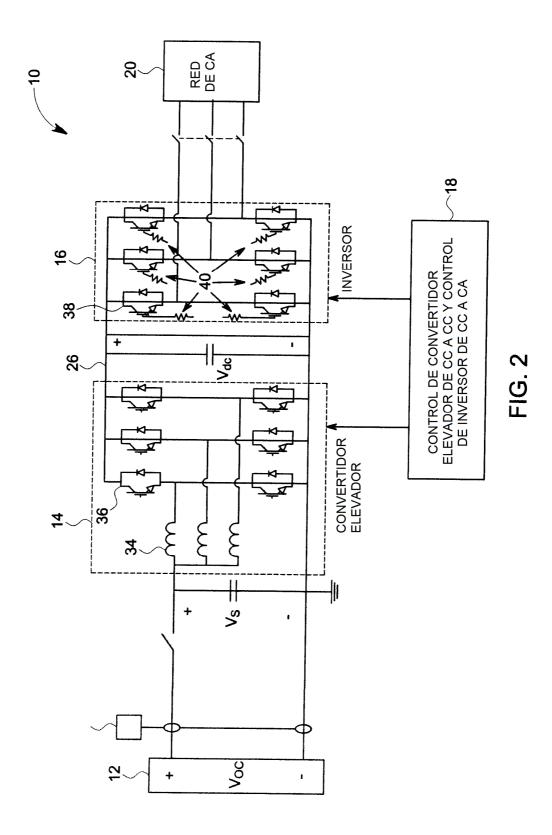

- La Figura 2 ilustra una vista más detallada del sistema inversor FV mostrado en la Figura 1;

20

25

30

35

40

45

50

55

60

65

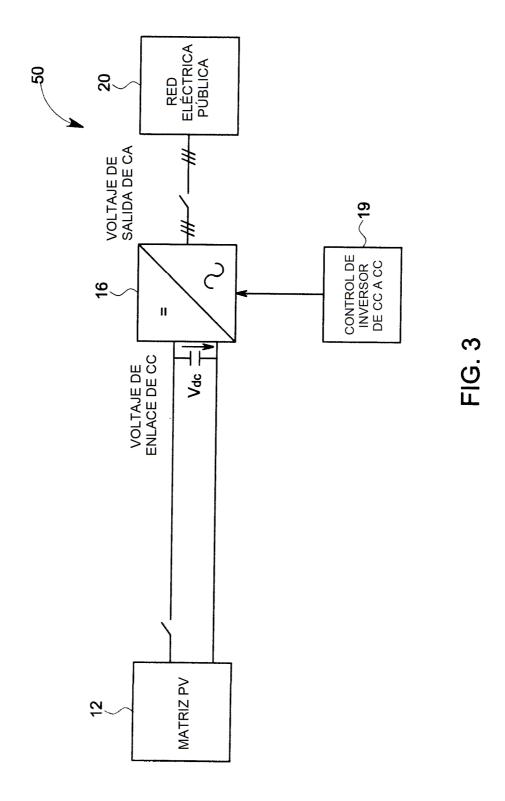

- La Figura 3 es un diagrama de bloques que ilustra un sistema inversor FV de acuerdo con otra realización;

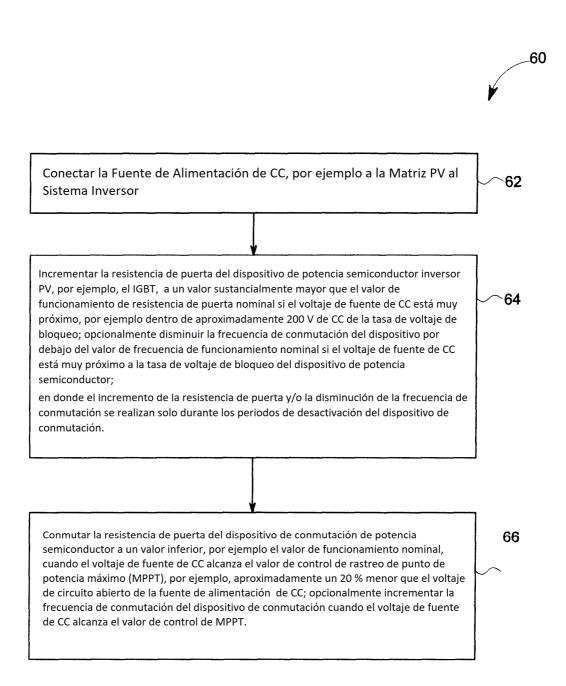

- La Figura 4 es un diagrama de flujo que ilustra un método de funcionamiento de los sistemas FV mostrados en las Figuras 1-3 de acuerdo con una realización; y

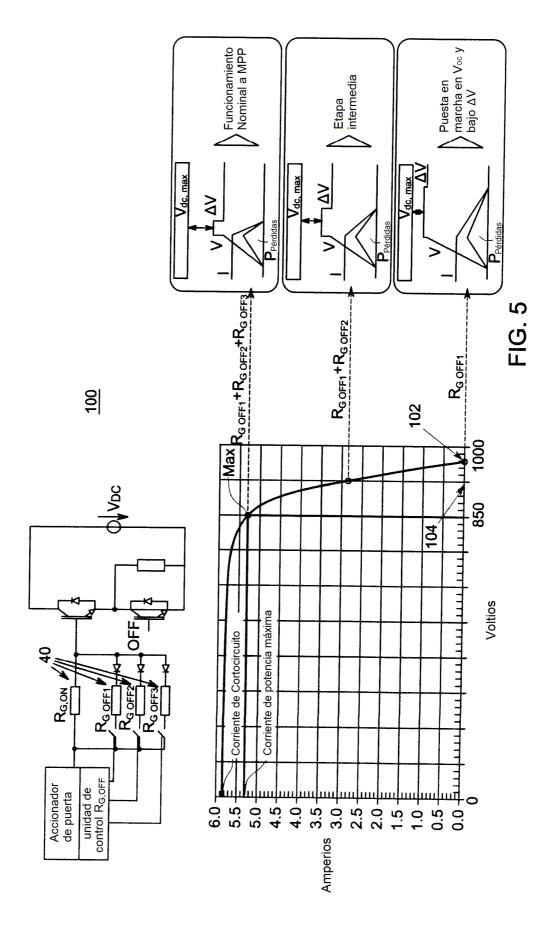

- La Figura 5 ilustra un sistema de control de puerta de mantenimiento de voltaje de acuerdo con una realización.

Aunque las figuras de dibujos identificadas anteriormente exponen realizaciones alternativas, también se contemplan otras realizaciones de la presente invención, como se expone en la descripción. En todos los casos, esta exposición presenta realizaciones ilustradas de la presente invención a modo de representación y no de limitación. Se pueden concebir numerosas otras modificaciones y realizaciones por los expertos en la técnica que caigan dentro del alcance y del fundamento de los principios de esta invención.

La Figura 1 representa un diagrama de bloques de un sistema inversor de potencia FV de dos etapas 10 utilizado para convertir potencia de corriente continua 22 generada por una matriz FV 12 en potencia de corriente alterna 28 adecuada para alimentar una red de potencia de corriente alterna 20. La primera etapa del sistema inversor de potencia 10 puede incluir un convertidor de corriente continua a corriente continua 14, tal como un convertidor elevador, que proporciona potencia de corriente continua 24 al enlace de corriente continua 26. El enlace de corriente continua 26 conecta el convertidor de corriente continua a corriente continua 14 a un inversor 16 que funciona como la segunda etapa del sistema inversor FV 10. El inversor 16 convierte la potencia de corriente continua 24 en el enlace de corriente continua 26 a potencia de corriente alterna 28 adecuada para ser suministrada a una red de potencia de corriente alterna 20. El convertidor de corriente continua a corriente continua 14 puede ser una parte de, o integral con, el inversor 16 o puede ser una estructura separada independiente del inversor 16. Además, más de un convertidor 14 puede ser conectado al mismo inversor 16 a través de uno o más enlaces de corriente continua.

El sistema inversor FV 10 incluye un sistema de control 16 que está configurado para controlar tanto el convertidor elevador de corriente continua a corriente continua 14 como el inversor de corriente continua a corriente alterna 16. Por ejemplo, el sistema de control 18 puede estar configurado para regular la salida del convertidor de corriente continua a corriente continua 14 de conformidad con un método de control que ajusta el ciclo de trabajo (velocidad de conmutación) de los dispositivos de conmutación (IGTBs u otros dispositivos electrónicos de potencia) utilizados en el convertidor de corriente continua a corriente continua 14. El sistema de control 18 también puede estar configurado para regular la salida del inversor 16 variando los comandos de modulación proporcionados al inversor 16. Los comandos de modulación controlan la modulación de anchura de pulso del inversor 16 y pueden ser utilizados para variar la potencia de salida real y reactiva del inversor 16. El sistema de control 18 puede ser independiente del convertidor elevador de corriente continua a corriente continua 14 y del inversor de corriente continua a corriente alterna 16 o puede estar integrado en una o ambas de las respectivas etapas del sistema 14, 16

Cuando el sistema inversor FV 10 está funcionando en condiciones de estado constantes, sistema de control 18 puede regular el voltaje de enlace de corriente continua 24 del enlace de corriente continua 26 (y, correspondientemente el voltaje de fuente de matriz FV de la matriz FV 12) ajustando la salida de corriente alterna del inversor 16. Por ejemplo, el sistema de control 18 puede regular el voltaje de enlace de corriente continua 24 del enlace de corriente continua 26 controlando las salidas de corriente alterna del inversor 16. En condiciones de estado estables, el inversor 16 es típicamente controlado para proporcionar flujo de potencia real (es decir, la parte real del producto vector del voltaje de corriente alterna de salida de inversor y la corriente alterna de salida de

inversor) a la red de corriente alterna 20 que es igual a la potencia suministrada al enlace de corriente continua 26 por el convertidor de corriente continua a corriente continua 14. La variación de la corriente alterna de salida del inversor 16 dará lugar a un cambio en el voltaje de corriente alterna de salida del inversor 16, en base a la impedancia de uno o más transformadores de salida y de la red eléctrica pública 20. El ajuste en el voltaje de corriente alterna de salida del inversor 16 correspondientemente inducirá un cambio en el voltaje de enlace de corriente continua 24 del enlace de corriente continua 26.

En situaciones en las que es necesario adaptar una matriz FV 12 (u otra fuente de alimentación de corriente continua) que tenga un voltaje de circuito abierto elevado, es deseable mantener el voltaje de enlace de corriente continua 24 menor que el voltaje de circuito abierto de la matriz FV 12. Manteniendo el voltaje de enlace de corriente continua 24 menor que el voltaje de circuito abierto de la matriz FV 12, el voltaje de fuente de matriz FV proporcionado por la matriz FV 12 al sistema inversor FV 10 también se puede mantener menor que el voltaje de circuito abierto de la matriz FV 12, tal como en el voltaje de potencia máximo de la matriz FV 12. En condiciones de estado constante, el sistema de control 18 puede regular el voltaje de enlace de corriente continua 24 para que sea menor que el voltaje de circuito abierto de la matriz FV 12 controlando la salida del inversor 16. Poniendo en marcha un sistema de inversor FV cuando el voltaje de circuito abierto de la matriz FV conectado está muy próximo a la tasa de voltaje de bloqueo de los dispositivos de potencia semiconductores de inversor FV, por ejemplo el voltaje de circuito abierto de matriz es de 1000 V de corriente continua y el voltaje de bloqueo de los dispositivos semiconductores es de 1200 V de corriente continua puede sin embargo ser problemático debido al exceso de voltaje de enlace de corriente continua.

La Figura 2 ilustra el sistema de inversor FV 10 mostrado en la Figura 1 modificado con resistencias limitantes de corriente de puerta 40 de dispositivo semiconductor de potencia 38. Un factor limitante cuando se pone en marcha el sistema de inversor FV 10 es el exceso de voltaje de corriente continua en la desactivación de los dispositivos de potencia semiconductores 38 que pueden comprender, por ejemplo, transistores bipolares de puerta aislada (IGBTs). El exceso de voltaje de enlace de corriente continua 26 está generalmente representado por el exceso de voltaje de corriente continua por tanto realmente no es dependiente de la magnitud de la corriente, sino de la velocidad de crecimiento de la corriente y la inductancia en el recorrido de comunicación. Este exceso de voltaje es solo un problema en la desactivación de los dispositivos IGBT 38. La activación de los dispositivos IGBT 38 no presenta problemas de exceso de voltaje.

Los presentes inventores reconocieron por sí mismos que operando un sistema inversor FV tal como el sistema inversor FV 10 mostrado en la Figura 1 cuando el voltaje de circuito abierto de la matriz FV conectada 12 es muy próximo a la tasa de voltaje de bloqueo del dispositivo de potencia semiconductor inversor 38, por ejemplo el voltaje de circuito abierto de matriz es de 1000 V de corriente continua y la tasa de voltaje de bloqueo del dispositivo de potencia semiconductor 38 es de 1200 V de corriente continua, es posible si las corrientes del dispositivo de potencia semiconductor son desactivadas a una velocidad di/dt muy baja por medio de resistencias de puerta grandes 40 tales como las mostradas en la Figura 2. Los presentes inventores reconocieron además que operando los dispositivos de potencia semiconductores 38 en combinación con una resistencia de puerta grande 40 se proporciona ventajosamente la deseada velocidad di/dt baja, pero en un nivel indeseable de eficiencia de funcionamiento del dispositivo de potencia 38; y que las anteriores pérdidas indeseables pueden ser reducidas a través de una reducción de la corriente y de la frecuencia de conmutación durante este modo de funcionamiento que dure un periodo muy corto de tiempo para una matriz FV 12.

De acuerdo con una realización, la resistencia(s) de puerta de valor elevado 40 son conmutadas de nuevo a un valor de resistencia nominal más pequeño cuando el voltaje de matriz FV alcanza su voltaje de punto de potencia máximo (MPP), que es aproximadamente un 20 % menor que el voltaje de circuito abierto de la matriz FV 12. De acuerdo con otra realización, la resistencia(s) de puerta 40 comprenden dispositivos de resistencia variable que reducen de forma lineal o no lineal el valor de resistencia de puerta del dispositivo de potencia semiconductor a medida que el voltaje de matriz FV continua cayendo en un valor que se aproxima al voltaje MPP. La Figura 5, por ejemplo, ilustra una arquitectura de control de puerta de mantenimiento de voltaje 100 que opera para reducir las resistencias de puerta de dispositivo de conmutación 40 de una manera por etapas durante las condiciones de puesta en marcha a medida que el voltaje de puerta se reduce desde un voltaje de circuito abierto inicial 102 al voltaje MPP 104 de acuerdo con una realización.

Aunque la Figura 2 ilustra una salida de corriente alterna de tres fases para el inversor 16, los expertos en la técnica, utilizando las revelaciones proporcionadas en la presente memoria, entenderán fácilmente que el inversor 16 puede proporcionar de manera similar una salida de corriente alterna de una única fase u otra salida de corriente alterna de múltiples fases según se desee sin desviarse del alcance la presente invención. El inversor 16 utiliza uno o más circuitos de puente de inversor que incluye dispositivos de potencia 38, tales como IGBTs y diodos que son utilizados para convertir la potencia de corriente continua en el enlace de corriente continua 26 a una onda de corriente alterna adecuada. Por ejemplo, en ciertas realizaciones, el inversor 16 utiliza modulación de anchura de pulso (PWM) para sintetizar un voltaje de corriente alterna de salida a la frecuencia de red de corriente alterna. La salida del inversor 16 puede ser controlada proporcionando comandos de temporización de puerta a los IGTBs 38 de los circuitos de puente de inversor del inversor 16 de acuerdo con las técnicas de control PWM conocidas. La

corriente alterna de salida que fluye desde el inversor 16 tiene componentes en la frecuencia de corte PWM y en la frecuencia de red.

El sistema inversor FV 10 también puede incluir un sensor de voltaje de matriz FV 42. El sensor de voltaje de matriz FV 42 monitoriza el voltaje de la matriz FV 12 y proporciona señales de retroalimentación para el sistema de control 18. El sistema de control 18 puede realizar ajustes en la resistencia de puerta 40 del dispositivo de potencia semiconductor 38 u otros parámetros de funcionamiento del sistema inversor FV 10, por ejemplo la frecuencia de conmutación del dispositivo de potencia semiconductor 38 basada en el voltaje de matriz FV detectado por el sensor de voltaje de matriz FV 42.

10

15

20

5

La Figura 3 es un diagrama de bloques simplificado que ilustra el sistema inversor FV 50 de acuerdo con otra realización. El sistema inversor 50 es similar al sistema inversor FV 10, excepto en que el sistema inversor FV 50 no emplea a un convertidor de corriente continua a corriente continua tal como el convertidor elevador 14 descrito en la presente memoria con referencia a las Figuras 1 y 2. Se puede observar que el sistema inversor FV 50 incluye una unidad de control de inversor de corriente continua a corriente alterna 19. De acuerdo con una realización, la unidad de control de inversor 19 está configurada para controlar la frecuencia de conmutación de los dispositivos de potencia semiconductores de inversor 38 y también para controlar el valor de resistencia de puerta para cada dispositivo de potencia semiconductor 38. De acuerdo con un aspecto, la frecuencia de conmutación es reducida por debajo de su valor de funcionamiento normal y la resistencia de puerta es incrementada por encima de su valor de funcionamiento normal cuando el voltaje de circuito abierto de la matriz FV 12 está muy próximo a la tasa de voltaje de bloqueo del dispositivo de potencia semiconductor, por ejemplo, el voltaje de circuito abierto de matriz es de 1000 V de corriente continua y el voltaje de bloqueo de los dispositivos de potencia semiconductores son 1200 V de corriente continua. De acuerdo con una realización, cuando el voltaje generado por la matriz FV 12 alcanza el voltaje MPP, que es aproximadamente 20 % menor que el voltaje de circuito abierto de la matriz FV 12, la resistencia de desconexión de puerta 40 empleada durante la desconexión del dispositivo de potencia semiconductor 38 es de nuevo conmutada a un valor menor por medio de la unidad de control 19. De acuerdo con otra realización, una o más resistencias de puerta 40 comprenden un dispositivo de resistencia variable que reduce el valor en respuesta a las señales recibidas desde la unidad de control 19 a medida que se reduce el valor de salida de voltaje de matriz

30

25

La Figura 4 es un diagrama de flujo que ilustra un procedimiento de puesta en marcha 60 para los sistemas convertidores de potencia 1, 50 de acuerdo con una realización. El proceso de puesta en marcha 60 evita de manera ventajosa cualesquiera requerimientos de hardware adicional necesarios para reducir el voltaje de la matriz FV 12 durante las condiciones de puesta en marcha. El proceso de puesta en marcha 60 inválida además de manera ventajosa la necesidad de utilizar dispositivos de potencia semiconductores con voltajes de bloqueo en mayores rangos, por ejemplo IGTBs de 1700 V, que reducen la eficiencia y aumentan el coste del sistema.

35

40

Continuando con la referencia a la Figura 4, el proceso de puesta en marcha 60 comienza conectando la fuente de voltaje de corriente continua, por ejemplo, la matriz FV 12, al sistema inversor FV 10, 50 como se representa en la etapa 62. El voltaje de enlace de corriente continua es preferiblemente menor que el voltaje de circuito abierto Voc de la matriz FV 12. De acuerdo con una realización, el controlador 18, 19 puede operar el enlace de corriente continua en un primer voltaje de enlace de corriente continua controlando la salida de corriente alterna del inversor 16. El sensor(es) de voltaje de matriz FV 12 está funcionando en un voltaje de circuito abierto o en otro voltaje.

45

50

Después de conectar la matriz FV 12 al sistema inversor FV 10, 50, el controlador 18, 19 funciona para incrementar rápidamente la resistencia de desactivación de puerta 40 de cada dispositivo de potencia semiconductor, por ejemplo, IGTBs, durante el periodo de puesta en marcha, hasta un valor que es mayor que su valor de funcionamiento nominal si el voltaje de matriz FV monitorizado está muy próximo a la tasa de voltaje de bloqueo del dispositivo de potencia semiconductor, como se representa en la etapa 64. De acuerdo con una realización, la frecuencia de conmutación del dispositivo de potencia semiconductor durante el respectivo periodo de puesta en marcha es también reducida a un valor que es menor que su valor de funcionamiento nominal si el voltaje de matriz FV monitorizado está muy próximo a la tasa de voltaje de bloqueo del dispositivo de potencia semiconductor.

55

Después de alcanzar el voltaje de rastreo MPP de matriz FV que es aproximadamente un 20 % menor que el voltaje de circuito abierto de la matriz FV, el controlador 18, 19 opera para conmutar la correspondiente resistencia(s) de puerta de desactivación 40 de nuevo a un valor de funcionamiento nominal más pequeño de acuerdo con una realización, como se representa en la etapa 66. De acuerdo con una realización, el controlador 18, 19 rastreará el voltaje de matriz FV para reducir de forma lineal o no lineal la correspondiente resistencia(s) de puerta 40 a medida que el voltaje de matriz FV continúa para reducir de valor el voltaje MPP de aproximación.

60

65

Los expertos en la técnica apreciarán fácilmente que la resistencia de puerta del dispositivo de conmutación de potencia semiconductor y las frecuencias de conmutación dependerán de la aplicación particular, de la arquitectura de sistema, y del dispositivo(s) de conmutación de potencia semiconductor empleado en el sistema inversor de potencia. Las características de conmutación y la resistencia de puerta se pueden realizar con o sin el uso de software de algoritmo, dependiendo de la aplicación particular. El software de algoritmo, si se emplea, residiría

dentro del controlador 18, 19 de acuerdo con una realización. De acuerdo con una realización, el controlador 18, 19 está configurado para cambiar la resistencia de desactivación de puerta para cada dispositivo de conmutación semiconductor de potencia 38 en caso de vector cero del SVM (modulador de vector de espacio). El vector cero, como se ha utilizado en la presente memoria, está definido como la configuración de conmutación de los dispositivos semiconductores de potencia 38 en el inversor de corriente continua a corriente alterna 16 que proporciona voltaje cero en la salida del inversor (por ejemplo, un vector cero positivo en un inversor de corriente continua a corriente alterna de los niveles de tres fases ocurre cuando todos los IGBTs superiores son activados y los IGBTs inferiores son desactivados. Vector cero negativo sucederá cuando todos los IGBTs superiores son desactivados y todos los IGBTs inferiores son activados). De acuerdo con otra realización, el controlador 18, 19 está además configurado para incrementar la resistencia de desconexión de puerta durante una carrera de voltaje cero/bajo a través de un evento (ZVRT/LVRT) del inversor de corriente continua a corriente alterna 16.

5

10

#### REIVINDICACIONES

- 1. Un sistema inversor de potencia (10), que comprende:

- 5 un inversor de corriente continua la corriente alterna (16) que comprende una pluralidad de dispositivos de conmutación semiconductores de potencia (38); y

- un enlace de corriente continua (26) que conecta selectivamente potencia de corriente continua al inversor (16); caracterizado por

- un controlador (18) configurado para incrementar una resistencia de desactivación de puerta para cada uno de los dispositivos de conmutación semiconductores de potencia (38) durante los periodos de puesta en marcha del sistema inversor (10), de manera que el voltaje de enlace de corriente continua (26) no excede las tasas de voltaje de bloqueo del dispositivo de conmutación semiconductor de potencia (38) durante los correspondientes periodos de desactivación de conmutación, en donde un periodo de puesta en marcha es el tiempo requerido para llevar un correspondiente voltaje de fuente (12) de potencia de corriente continua desde un voltaje de circuito abierto a un voltaje predeterminado que constituye una condición de funcionamiento segura para la pluralidad de los dispositivos de conmutación semiconductores de potencia (38).

- 2. El sistema inversor de potencia (10) de acuerdo con la reivindicación 1, en el que el voltaje predeterminado comprende el voltaje de punto de potencia máximo de fuente de alimentación de corriente continua.

- 3. El sistema inversor de potencia (10) de acuerdo con cualquier reivindicación precedente, que comprende una matriz fotovoltaica (12) configurada para generar potencia de corriente continua.

- 4. El sistema inversor de potencia (10) de acuerdo con cualquier reivindicación precedente, en el que el controlador (18) está configurado además para incrementar la resistencia de desactivación de puerta (40) solo cuando el voltaje de enlace de corriente continua (26) está dentro de un valor de voltaje mínimo y máximo en base a la tasa de voltaje de bloqueo de los dispositivos de conmutación semiconductores de potencia (38).

- 30 5. El sistema inversor de potencia (10) de acuerdo con cualquier reivindicación precedente, en el que los dispositivos de conmutación semiconductores de potencia (38) comprenden transistores bipolares de puerta aislada.

- 6. El sistema inversor de potencia (10) de acuerdo con cualquier reivindicación precedente, en el que el controlador (18) está además configurado para disminuir la frecuencia de conmutación del inversor de corriente continua a corriente alterna (16) durante los periodos de puesta en marcha del sistema inversor de potencia (10).

- 7. El sistema inversor de potencia (10) de acuerdo con cualquier reivindicación precedente, en el que el controlador (18) está además configurado para controlar la resistencia de desactivación de puerta (40) para cada dispositivo de conmutación semiconductor de potencia (38) de una manera por etapas o sin etapas en base nivel de voltaje de fuente de alimentación de corriente continua (12).

- 8. El sistema inversor de potencia (10) de acuerdo con cualquier reivindicación precedente, en el que el controlador (18) está configurado además para cambiar la resistencia de desactivación de puerta (40) para cada dispositivo de conmutación semiconductor de potencia (38) en caso de vector cero de un correspondiente modulador de vector de espacio, en donde el vector cero se define como la configuración de los dispositivos semiconductores de potencia (38) en un inversor de corriente continua a corriente alterna (16) que proporciona voltaje cero en la salida del inversor (16).

- 9. El sistema inversor de potencia (10) de acuerdo con cualquier reivindicación precedente, en donde el controlador (18) está además configurado para incrementar la resistencia desactivación de porta (40) durante una carrera de voltaje cero/bajo a través de un evento (ZVRT/LVRT) del inversor de corriente continua a corriente alterna (16).

- 10. Un método de funcionamiento de un sistema inversor de potencia, comprendiendo el método:

- proporcionar un controlador de inversor y un inversor que comprende una pluralidad de dispositivos de conmutación semiconductores de potencia; y

conectar la fuente de voltaje de corriente continua al inversor;

#### caracterizado por

35

40

45

60

después de conectar la fuente de voltaje de corriente continua al inversor, aumentar una resistencia de desactivación de puerta para cada uno de los dispositivos de conmutación de potencia semiconductores durante un correspondiente periodo de puesta en marcha de inversor, de manera que el voltaje de fuente no excede una tasa de voltaje de bloqueo del dispositivo de conmutación semiconductor de potencia durante los correspondientes periodos de desactivación de conmutación de semiconductor de potencia, en donde el periodo de puesta en marcha es el tiempo requerido para llevar el voltaje de fuente de corriente continua

desde un voltaje de circuito abierto a un voltaje predeterminado que constituye una conducción de funcionamiento segura para la pluralidad de dispositivos de conmutación semiconductores de potencia.

11. El método de acuerdo con la reivindicación 10, en el que el voltaje predeterminado comprende el voltaje de punto de potencia máximo de fuente de alimentación de corriente continua.

5

12. El método de acuerdo con la reivindicación 10 o la reivindicación 11, en el que la fuente de voltaje de corriente continua comprende una matriz fotovoltaica.

9

FIG. 4