# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

(1) Número de publicación: 2812556

51 Int. CI.:

H01L 25/065 (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

86 Fecha de presentación y número de la solicitud internacional: 24.06.2009 PCT/US2009/048372

(87) Fecha y número de publicación internacional: 07.01.2010 WO10002645

(96) Fecha de presentación y número de la solicitud europea: 24.06.2009 E 09774097 (1)

(97) Fecha y número de publicación de la concesión europea: 20.05.2020 EP 2311088

(54) Título: Interconexión de puente con vías a través de silicio

(30) Prioridad:

30.06.2008 US 164331

Fecha de publicación y mención en BOPI de la traducción de la patente: 17.03.2021

(73) Titular/es:

QUALCOMM INCORPORATED (100.0%) Attn: International IP Administration 5775 Morehouse Drive San Diego, CA 92121, US

(72) Inventor/es:

CHANDRASEKARAN, ARVIND

(74) Agente/Representante:

FORTEA LAGUNA, Juan José

#### **DESCRIPCIÓN**

Interconexión de puente con vías a través de silicio

#### 5 CAMPO TÉCNICO

[0001] La presente divulgación se refiere a la encapsulación de circuitos integrados (CI), y más específicamente a las interconexiones de puente entre circuitos integrados de lado a lado dentro de un encapsulado con sustrato.

#### 10 ANTECEDENTES

25

30

35

40

45

50

55

60

65

[0002] En la encapsulación de CI, existe la necesidad de proporcionar dados semiconductores en una configuración de lado a lado dentro de un encapsulado e interconectarlos. El encapsulado puede ser, por ejemplo, un encapsulado de bastidor de conductores.

[0003] En una configuración, se encapsulan dados semiconductores con el lado activo de cada dado orientado hacia afuera de la base de encapsulado. La interconexión entre dados se logra por unión con hilos. Sin embargo, las reglas de diseño para la interconexión de ensamblaje pueden estar limitadas por las dimensiones del diámetro de los hilos y la herramienta capilar en la unión con hilos, lo que requiere almohadillas de unión que sean lo suficientemente grandes y estén lo suficientemente espaciadas entre sí para acomodar las dimensiones. Por tanto, el número de interconexiones está limitado por el tamaño de las interconexiones. Además, la inductancia de los conductores en la unión con hilos de dado a dado puede limitar el rendimiento del dispositivo encapsulado. Además, un hilo de oro es una elección convencional para la unión con hilos, lo que incrementa significativamente el coste neto del encapsulado.

**[0004]** En otra configuración, la encapsulación con bolas de soldadura de chip boca abajo la región del dispositivo activo del dado está en la superficie orientada hacia el sustrato de montaje del encapsulado, por ejemplo, hacia abajo. En esta configuración, la densidad de interconexión entre dados adyacentes también está limitada por los requisitos de tamaño de las almohadillas de contacto.

[0005] La patente de Estados Unidos n. 5,225,633 divulga la interconexión de dos dados semiconductores en una configuración de lado a lado usando elementos de puente. Cada elemento de puente comprende un dado rígido de silicio que soporta conductores soporte de conducción sobresalientes. El puente se coloca en un espacio entre dos dados semiconductores, y la extensión del saliente de cada conductor soporte y el posicionamiento adyacente se seleccionan para proporcionar un acoplamiento apropiado con almohadillas de unión posicionadas en cada uno de los dados semiconductores que se van a interconectar. Sin embargo, no se divulga ningún procedimiento de formación de conductores soporte o de su disposición en el puente de silicio. Además, la manipulación y el ensamblaje de los conductores soporte puede ser difícil, y el puente ocupa espacio entre los dos dados. Además, como el oro es un metal de interconexión preferente, existe un impacto sobre el coste del material del encapsulado ensamblado.

**[0006]** Por lo tanto, existe la necesidad de obtener un sistema de interconexión de encapsulación entre dados semiconductores adyacentes que simplifique el procedimiento de ensamblaje, reduzca el coste de los materiales de interconexión y posibilite la interconexión entre chips con una distancia entre centros más fina de lo que es convencionalmente permisible con la unión con hilos e interconexiones de conductores soporte equivalentes.

[0007] La solicitud de patente US 2004/0184250 se refiere a un encapsulado apilado con múltiples chips que comprende un sustrato, un primer chip inferior, un segundo chip inferior, un chip superior y un soporte. El sustrato tiene una superficie superior, y el primer chip inferior y el segundo chip inferior están dispuestos en la superficie superior del sustrato y conectados eléctricamente al sustrato. El soporte está dispuesto y conectado eléctricamente al primer chip inferior y al segundo chip inferior simultáneamente, y el chip superior está montado en el soporte. Además, el chip superior está conectado eléctricamente al sustrato a través del soporte, el primer chip inferior o el segundo chip inferior.

[0008] La solicitud de patente US 2008/0105987 se refiere a un dispositivo semiconductor que tiene un intermediador formado en un chip semiconductor. El chip semiconductor incluye un sustrato que tiene electrodos externos usados para la transferencia de señales o suministro de energía con respecto al exterior y almohadillas para el suministro de energía dispuestas en un área en el sustrato en la que los electrodos externos no están formados y conectados a los electrodos externos por medio de hilos en la superficie principal del mismo. El intermediador tiene una capa conductora dispuesta en parte de la superficie principal del chip semiconductor en la que las almohadillas para el suministro de energía no están formadas, conectada al chip semiconductor por medio de clavijas de conexión y conectada a los electrodos externos para el suministro de energía por medio de hilos.

[0009] La solicitud de patente US2008/0084725 A1 se refiere a disposiciones de chips electrónicos, incluyendo una disposición de chips tridimensional que incluye un administrador de memoria. La disposición de chips tiene un

sustrato base en el que se disponen los dados lógicos. Se apilan tres dados de memoria en los dados lógicos. Una interfaz de control en el sustrato base conecta los dados lógicos.

#### BREVE EXPLICACIÓN

5

10

15

25

30

35

40

45

50

55

60

65

[0010] Los aspectos de la presente invención se exponen en las reivindicaciones adjuntas.

[0011] Los rasgos característicos y ventajas adicionales de la invención se describirán a continuación en el presente documento, que forman el objeto de las reivindicaciones de la invención. Se debe apreciar por los expertos en la técnica que la concepción y modo de realización específico divulgados se pueden utilizar fácilmente como una base para modificar o diseñar otras estructuras para llevar a cabo los mismos propósitos de la presente invención. También se debe comprender por los expertos en la técnica que dichas construcciones equivalentes no se apartan del espíritu y alcance de la invención como se expone en las reivindicaciones adjuntas. Los rasgos característicos novedosos que se cree que son característicos de la invención, tanto en lo que respecta a su organización como a su procedimiento de funcionamiento, conjuntamente con otros objetos y ventajas, se entenderán mejor a partir de la siguiente descripción cuando se consideren en relación con las figuras adjuntas. Se ha de entender expresamente, sin embargo, que cada una de las figuras se proporciona solo con el propósito de ilustración y descripción, y no se pretenden como una definición de los límites de la presente invención.

## 20 BREVE DESCRIPCIÓN DE LOS DIBUJOS

[0012] Para un entendimiento más completo de la presente invención, ahora se hace referencia a las siguientes descripciones tomadas junto con los dibujos adjuntos, en los que:

La FIGURA 1 muestra un sistema de comunicación inalámbrica ejemplar en el que se pueden emplear de forma ventajosa modos de realización de la invención.

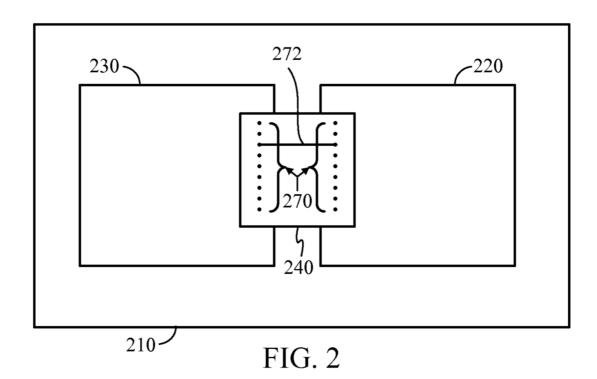

La FIGURA 2 ilustra una vista en planta de una interconexión de puente con TSV de acuerdo con un modo de realización de la invención.

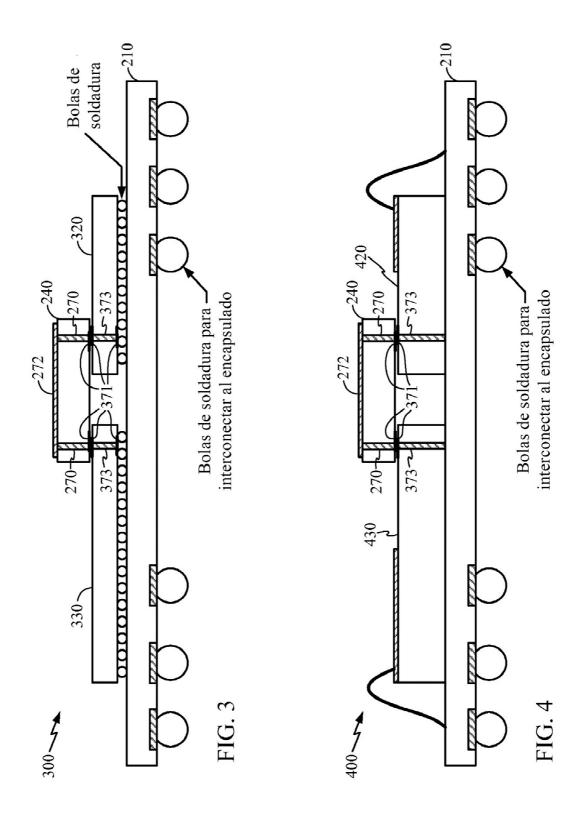

La FIGURA 3 es una vista en sección transversal en despiece ejemplar de un modo de realización de una interconexión de puente entre dos dados de chip boca abajo.

La FIGURA 4 es una vista en sección transversal en despiece ejemplar de un modo de realización de una interconexión de puente entre dos dados de unión con hilos.

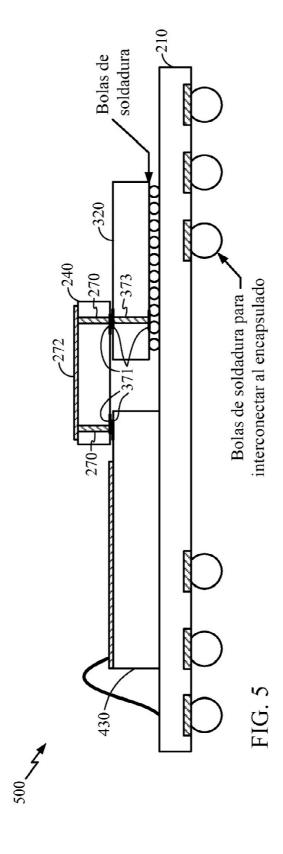

La FIGURA 5 es una vista en sección transversal en despiece ejemplar de un modo de realización de una interconexión de puente entre un dado de chip boca abajo y un dado de unión con hilos.

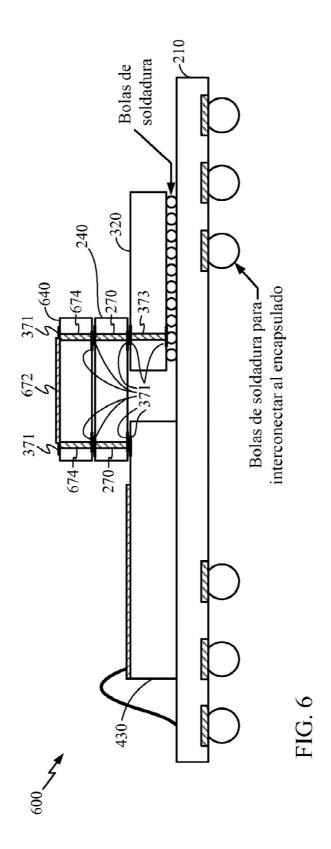

La FIGURA 6 es una vista en sección transversal en despiece ejemplar de un ejemplo, que no se encuentra dentro del alcance de la invención reivindicada, en la que se apilan dados adicionales en una interconexión de puente.

#### DESCRIPCIÓN DETALLADA

[0013] Se divulgan procedimientos y estructuras para conectar dos dados semiconductores (chips), que se colocan en una configuración de lado a lado en un encapsulado basado en sustrato. Las conexiones se pueden conseguir usando un dado de puente de interconexión semiconductor (típicamente silicio) para hacer contacto con ambos dados de lado a lado. El dado de puente de interconexión tiene vías a través de silicio para conectar las almohadillas de contacto en cada uno de los dados a la superficie opuesta del dado de puente de interconexión. Están formadas líneas de interconexión en el dado de puente de interconexión para completar las conexiones entre las vías a través de silicio.

[0014] La FIGURA 1 muestra un sistema de comunicación inalámbrica 100 ejemplar en el que se puede emplear de forma ventajosa un modo de realización de la invención. Con propósitos de ilustración, la FIGURA 1 muestra tres unidades a distancia 120, 130 y 150 y dos estaciones base 140. Se reconocerá que los sistemas de comunicación inalámbrica típicos pueden tener muchas más unidades a distancia y estaciones base. Las unidades a distancia 120, 130 y 150 incluyen encapsulados con múltiples chips con interconexiones de puente con vías a través de silicio (TSV) 125A, 125B y 125C, lo que es un modo de realización de la invención como se analiza más adelante. La FIGURA 1 muestra señales de enlace directo 180 desde las estaciones base 140 y las unidades a distancia 120, 130 y 150 y señales de enlace inverso 190 desde las unidades a distancia 120, 130 y 150 a las estaciones base 140.

**[0015]** En la FIGURA 1, la unidad a distancia 120 se muestra como un teléfono móvil, la unidad a distancia 130 se muestra como una un ordenador portátil y la unidad a distancia 150 se muestra como una unidad a distancia en una ubicación fija en un sistema de bucle local inalámbrico. Por ejemplo, las unidades a distancia pueden ser

teléfonos móviles, unidades de sistemas de comunicación personal (PCS) de mano, unidades de datos portátiles, tales como asistentes de datos personales o unidades de datos en una ubicación fija, tales como equipos de lectura de contadores. Aunque la FIGURA 1 ilustra unidades a distancia de acuerdo con las enseñanzas de la invención, la invención no se limita a estas unidades ilustradas ejemplares. La invención se puede emplear adecuadamente en cualquier dispositivo que incluya un encapsulado con múltiples chips que tenga chips en una configuración de lado a lado.

5

10

15

20

25

30

35

45

50

55

60

65

[0016] La FIGURA 2 ilustra una vista en planta de una configuración 200 de interconexión de puente con TSV de acuerdo con un modo de realización de la invención. La configuración 200 incluye un sustrato 210, que puede ser, por ejemplo, una placa de circuito impreso con sustrato orgánico o cerámico. Se pueden colocar dos o más dados, donde cada dado tenga un primer y un segundo lado, en el sustrato 210. Para una ilustración ejemplar, en referencia a la FIGURA 2, los dos dados 220 y 230 se muestran colocados en una configuración de lado a lado. Una superficie de los dados 220 y 230 se puede conectar al sustrato 210, y finalmente a los conductores del encapsulado.

[0017] Un dado de interconexión de puente 240 que tiene un primer y un segundo lado se solapa al menos parcialmente y se comunica eléctricamente con los dados 220 y 230. Las vías a través de silicio (TSV) 270 rellenas de metal conductor conectan el primer lado (que se muestra orientado hacia afuera de la página) del dado de interconexión de puente 240 a los circuitos activos en los dados 220 y 230. Las líneas de interconexión 272 en el primer lado del dado de interconexión de puente 240 completan, entonces, las conexiones entre los dados 220 y 230. Para diferentes aplicaciones funcionales, donde las funciones específicas de los dados 220 y 230 cambian, las líneas de interconexión 272 se pueden reconexionar apropiadamente y las TSV 270 se pueden reubicar por un cambio en las fotomáscaras y la fabricación al nivel de procesamiento a escala de oblea.

[0018] Además, las líneas de interconexión 272 pueden ser principalmente interconexiones de metal pasivo. Aunque no mostrado en la FIGURA 2, el primer lado del dado de interconexión de puente 240 puede incluir circuitos activos adicionales, no relacionados con la funcionalidad de interconexión.

[0019] Las líneas de interconexión 272 y/o circuitos en el dado de interconexión de puente 240 se pueden formar al nivel de oblea, incluyendo la formación de los orificios rellenos de metal TSV 270 usando procedimientos con semiconductores y de metalización convencionales, después de lo que la oblea se puede separar entonces en dados de interconexión de puente 240 individuales.

[0020] La FIGURA 3 es una vista en sección transversal en despiece ejemplar de un modo de realización de una configuración 300 de una interconexión de puente entre dos dados de chip boca abajo. Los circuitos activos del dado 320 y del dado 330 de chip boca abajo están en los segundos lados, orientados hacia el sustrato 210. Los dados 320 y 330 se pueden fijar al sustrato 210, por ejemplo, por unión con bolas de soldadura o procedimientos equivalentes usados en la encapsulación de circuitos integrados.

[0021] Están formadas vías a través de silicio (TSV) 373 a través del espesor de los dados 320 y 330 para proporcionar una interconexión metálica entre los primeros lados (mostrados orientados hacia arriba en la FIGURA 2) y los circuitos activos en los segundos lados de los dados 320 y 330.

[0022] Las almohadillas de contacto 371 en el segundo lado del dado de interconexión de puente 240 y los primeros lados de los dados 320 y 330 están alineados, y se pueden unir usando procedimientos tales como, por ejemplo, unión con bolas de soldadura y pasta conductora. Las almohadillas de contacto 371 formadas en los dados 320, 330 y 240 posibilitan el contacto conductor entre las TSV 270 y 373 correspondientes. En consecuencia, los circuitos activos en los dados 320 y 330 se conectan eléctricamente al primer lado del dado de interconexión de puente 240, donde la interconexión entre los circuitos activos se completa usando las líneas de interconexión 272. Las almohadillas de contacto 371 se muestran como que interconectan los circuitos activos y las bolas de soldadura.

[0023] La FIGURA 4 es una vista en sección transversal en despiece ejemplar de un modo de realización de una configuración 400 de una interconexión de puente entre dos dados de unión con hilos 420 y 430. El dado de interconexión de puente 240 puede ser sustancialmente el mismo que el dado de interconexión de puente 240 mostrado en la FIGURA 3. Es decir, el dado de interconexión de puente 240 de la FIGURA 4 puede tener los mismos rasgos característicos y disposición de las TSV 270, almohadillas de contacto 371, líneas de interconexión 272 y opcionalmente elementos de impedancia y/o dispositivos activos, también colocados en el primer lado del dado de interconexión de puente 240 de la FIGURA 3.

**[0024]** Los dados de unión con hilos semiconductores 420 y 430 tienen ambos un primer lado y un segundo lado, donde los segundos lados de los dados 420 y 430 se orientan hacia y están fijados al sustrato 210. La unión con hilos conecta las almohadillas de contacto en los primeros lados de los dados 420 y 430 a las almohadillas de contacto en el sustrato 210. Como en la configuración 300 de chip boca abajo de la FIGURA 3, los tres dados 420, 430 y 240 tienen almohadillas de contacto 371 en ubicaciones correspondientes para posibilitar la interconexión de los circuitos de los dados 420 y 430 a través del dado de interconexión de puente 240.

**[0025]** Los circuitos activos en los dados 420 y 430 están ubicados en la primera superficie (es decir, orientados hacia afuera del sustrato 210). En la configuración 400, debido a que los circuitos activos están en el primer lado, la inclusión de TSV 373 en los dados 420 y 430, como se muestra en la FIGURA 4, se puede incluir opcionalmente o puede que no se requiera.

[0026] La FIGURA 5 es una vista en sección transversal en despiece ejemplar de un modo de realización de una configuración 500 de una interconexión de puente entre el dado de chip boca abajo 320 y el dado de unión con hilos 430. Se puede realizar una compensación apropiada para las diferencias relativas en el espesor de los dados, la altura de la unión con bolas, etc., para posicionar los primeros lados de ambos dados 320 y 430 a la misma altura. La consideración de interfaces apropiadas entre los dados de chip boca abajo, de puente y de unión con hilos son las mismas como se describe con referencia a las FIGURAS 3 y 4. Por ejemplo, el dado de chip boca abajo 320 tiene circuitos activos dispuestos en el segundo lado (es decir, orientados hacia el sustrato 210) y puede requerir una pluralidad de TSV 373 conectadas a las almohadillas de contacto 371 en el primer lado para facilitar las conexiones al dado de interconexión de puente 240. El dado de unión con hilos 430, por otra parte, tiene circuitos activos dispuestos en el primer lado (es decir, orientados hacia afuera del sustrato 210) y puede no requerir las TSV 373. En cambio, las almohadillas de contacto 371 conectadas a los circuitos activos pueden ser suficientes.

[0027] La FIGURA 6 (que no se encuentra dentro del alcance de la invención reivindicada) es una es una vista en sección transversal ejemplar de un ejemplo de una configuración 600 en la que al menos uno o más dados 640 adicionales (donde, con propósitos ilustrativos, solo se muestra un dado 640) se apilan en el dado de interconexión de puente 240. El dado 640 adicional puede incluir una funcionalidad, tecnología de materiales u otra base para formar el dado 640 por separado de otros dados 320, 430 que contienen dispositivos activos. El dado de puente de interconexión 240 puede incluir almohadillas de contacto 371 en el primer lado para interconectarse con las almohadillas de contacto 371 correspondientes orientadas opuestas y ubicadas en el dado 640. El dado 640 puede incluir TSV 674 conectadas a las almohadillas de contacto 371 en ambos lados del dado 640 para proporcionar la interconexión entre el dado de puente de interconexión 240 y las líneas de interconexión 672 y/o circuitos funcionales en la superficie superior del dado 640. Los ejemplos de funcionalidad del dado 640 incluyen memoria, retraso, amplificadores, lógica, etc. Se puede considerar el apilamiento de dados 640 adicionales sobre el dado de puente de interconexión 240, de acuerdo con la funcionalidad, la encapsulación y otros objetivos deseados. Cuando se emplea la unión con bolas para interconectar almohadillas en un dado adyacente (apilado verticalmente), la disposición de los circuitos puede estar en el primer o bien en el segundo lado del dado 640.

[0028] Se pueden obtener numerosas ventajas de los modos de realización descritos. Al usar un dado de puente, los trazados de interconexión se pueden fabricar en cantidades a escala de oblea usando procedimientos con semiconductores. El espesor de la metalización puede ser del orden de unos pocos micrómetros o menos, con anchos de línea adecuados para nodos tecnológicos avanzados, tales como de 45 nm y menos. El metal puede ser uno distinto a oro. En comparación con la unión con hilos de oro entre sustratos, se pueden obtener ahorros sustanciales de material.

[0029] Además, la unión con hilos requiere un espacio mínimo entre las almohadillas de contacto adyacentes en un sustrato, por motivos debidos, al menos en parte, al tamaño de la punta capilar usada en la unión con hilos. Por el contrario, es posible una distancia entre centros muy fina de los trazados de interconexión en el dado de puente, haciendo posible las interconexiones densas. Además, con la unión con hilos, cada unión se consigue individualmente, mientras que con una interconexión de puente, se consiguen múltiples uniones con una colocación a nivel de chip y procedimientos de unión, tales como, por ejemplo, reflujo de soldadura.

[0030] Además, cuando se ha diseñado previamente una configuración con múltiples chips de lado a lado para la unión con hilos, se puede implementar de forma beneficiosa una interconexión de puente para reemplazar a la unión con hilos, mientras que se hace uso de las almohadillas de contacto existentes. Un reemplazo de la interconexión de puente por la unión con hilos reduce el número de etapas de ensamblaje de múltiples etapas de unión con hilos separadas a una única colocación de dados.

[0031] Todavía más, la unión con hilos típicamente implica un bucle en el arco del hilo entre dos almohadillas de unión además de una distancia mínima requerida entre las almohadillas de unión. Como resultado, la inductancia de los hilos puede degradar el rendimiento, especialmente en dispositivos de alta velocidad donde la impedancia inductiva se incrementa con la frecuencia. La radiación electromagnética de los conductores se puede detectar de forma no deseable en otra parte en los chips dentro del encapsulado. Con un dado de puente, los dados que se van a conectar se pueden colocar próximos entre sí, lo que reduce la radiación y lo que incrementa la eficacia de utilización del encapsulado. El dado de puente se puede fabricar bastante pequeño, con rutas de interconexión más cortas de forma correspondiente que las que se requerirían con las uniones con hilos.

[0032] Aún otra ventaja es la capacidad eficaz de incluir en un único encapsulado dos o más circuitos integrados que requieran diferentes materiales, flujos de procedimiento o nodos tecnológicos para optimizar el rendimiento a "nivel de sistema" dado por los beneficios personalizados de cada chip. Esto posibilita una funcionalidad de mayor nivel en un único encapsulado.

- [0033] Todavía otra ventaja es la capacidad de incluir una funcionalidad en el dado de puente, que no se puede posibilitar exclusivamente por unión con hilos.

- 5 **[0034]** Muchas de las mismas ventajas se aplican cuando se usa la unión de chips boca abajo para encapsular dados de circuitos integrados. Al implementar las TSV en dados de chip boca abajo, se pueden posibilitar las interconexiones con una distancia entre centros fina y la economía de espacio de las rutas de conexiones.

- [0035] Aunque la presente invención y sus ventajas se han descrito en detalle, se debe entender que se pueden realizar diversos cambios, sustituciones y alteraciones en el presente documento sin apartarse del alcance de la invención como se define por las reivindicaciones adjuntas. Por ejemplo, aunque se ha usado una operación de lectura en el análisis, se contempla que la invención se aplique igualmente a las operaciones de escritura. Por ejemplo, aunque que TSV sea un término común de la técnica en referencia a las vías en dados de silicio, se pueden formar vías en otros materiales, y, en particular, otros dados semiconductores, tales como GaAs, SiC, GaN u otros materiales adecuados. El término TSV se puede aplicar con aplicación a cualquiera de dichos materiales.

#### REIVINDICACIONES

un primer dado semiconductor (220; 320; 420) que tiene un primer lado y un segundo lado;

un segundo dado semiconductor (230; 330; 430), que tiene un primer lado y un segundo lado, provisto

Un sistema de interconexión de puente entre circuitos integrados (200; 300; 400), que comprende:

en una configuración de lado a lado con el primer dado semiconductor (220; 320; 420): 10 un dado semiconductor de puente (240), que tiene un primer lado y un segundo lado; estando dispuesto el segundo lado del dado semiconductor de puente (240) al menos parcialmente en los primeros lados del primer dado semiconductor (220; 320; 420) y el segundo dado semiconductor (230: 330: 430): 15 estando configurado el dado semiconductor de puente (240) para interconectar eléctricamente el primer dado semiconductor (220; 320; 420) y el segundo dado semiconductor (230; 330; 430); teniendo el dado semiconductor de puente (240) vías a través (270) de dado semiconductor de puente desde el primer lado del dado semiconductor de puente al segundo lado del dado 20 semiconductor de puente, caracterizado por que: estando las vías a través (270) de dado semiconductor de puente rellenas de metalizaciones para conectar líneas de interconexión (272) de metal pasivo en el primer lado del dado semiconductor 25 de puente (240) para posibilitar la interconexión. El sistema de la reivindicación 1, en el que al menos uno del primer dado semiconductor (220; 320; 420) y segundo dado semiconductor (230; 330; 430) comprende:

vías a través (273) de chip boca abajo desde el primer lado del dado semiconductor de chip boca abajo al segundo lado del dado semiconductor de chip boca abajo, estando las vías a través (373) de chip boca abajo rellenas de metalizaciones para conectar circuitos activos en el segundo lado del dado semiconductor de chip boca abajo (320, 330) a una o más almohadillas de contacto (371) en el primer lado del dado semiconductor de chip boca abajo.

un dado semiconductor de chip boca abajo (320, 330) que tiene circuitos dispuestos en el segundo lado;

40 **3.** El sistema de la reivindicación 2, en el que:

У

el primer dado semiconductor es el dado semiconductor de chip boca abajo (320) que tiene circuitos dispuestos en el segundo lado; y

el segundo dado de semiconductor es un dado de unión con hilos (430).

- 4. El sistema de la reivindicación 1, en el que al menos uno del primer dado semiconductor (220; 420) y segundo dado semiconductor (230; 430) comprende circuitos dispuestos en el primer lado del dado semiconductor.

- 5. El sistema de la reivindicación 1, que comprende además una o más almohadillas de contacto (371) en el primer lado del primer dado semiconductor (220; 320; 420) y el primer lado del segundo dado semiconductor (230; 330; 430).

- **6.** El sistema de la reivindicación 5, en el que el dado semiconductor de puente (240) comprende además:

una o más almohadillas de contacto (371) en el segundo lado del dado semiconductor de puente correspondientes a las vías a través (270) de dado semiconductor de puente y opuestas a y correspondientes a las una o más almohadillas de contacto (371) en los primeros lados del primer y/o segundo dado semiconductor.

7. El sistema de una cualquiera de las reivindicaciones precedentes, en el que el dado semiconductor de puente (240) se fabrica usando un flujo de procedimiento que es diferente de un flujo de procedimiento correspondiente al primer dado semiconductor (220; 320; 420) y/o el segundo dado semiconductor (230; 330; 430).

65

60

1.

5

30

35

45

8. El sistema de cualquier reivindicación precedente, que comprende además un encapsulado para contener los dados semiconductores (220; 320; 420, 230; 330; 430) y un sustrato (210) dispuesto dentro del encapsulado para recibir dados semiconductores (220; 320; 420, 230; 330; 430), en el que el primer dado semiconductor (220; 320; 420) está dispuesto en el sustrato (210) con el segundo lado orientado hacia el sustrato (210) y el segundo dado semiconductor (230; 330; 430) está dispuesto en el sustrato (210) con el segundo lado orientado hacia el sustrato (210).

5