OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11) Número de publicación: 2 535 779

21 Número de solicitud: 201331656

51 Int. Cl.:

**G06F 7/70** (2006.01)

(12)

#### SOLICITUD DE PATENTE

Α1

22) Fecha de presentación:

14.11.2013

(43) Fecha de publicación de la solicitud:

14.05.2015

(71) Solicitantes:

UNIVERSITAT DE LES ILLES BALEARS (100.0%) Ctra. de Valldemossa, km. 7,5 07071 Palma de Mallorca (Illes Balears) ES

(72) Inventor/es:

CANALS GUINAND, Vicente J.; MORRO GOMILA, Antoni; ROSSELLÓ SANZ, Josep L.; ALOMAR BARCELÓ, Miquel L. y OLIVER GELABERT, Antoni

(74) Agente/Representante:

TEMIÑO CENICEROS, Ignacio

54) Título: Sistemas digitales probabilísticos inmunes al ruido electromagnético

(57) Resumen:

Sistemas digitales probabilísticos inmunes al ruido electromagnético.

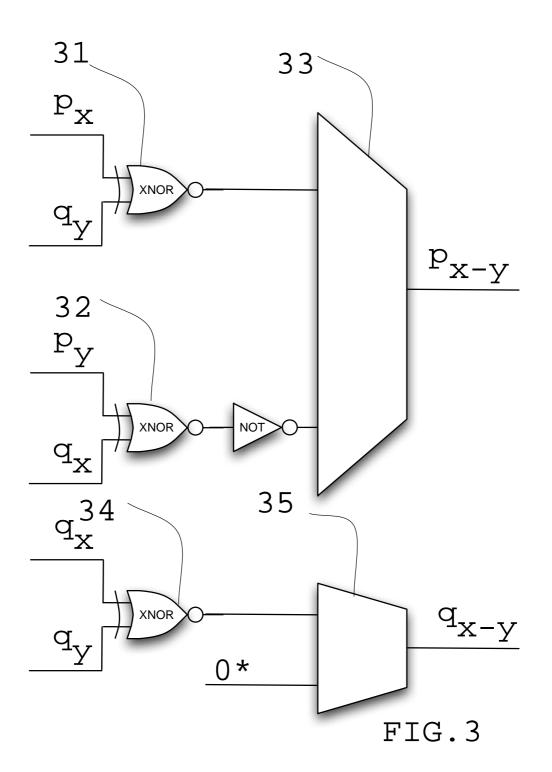

La invención se refiere a usos y a métodos basados en circuitos de lógica estocástica extendida (ESL) como medio de atenuación de ruido electromágnetico. Más concretamente, la invención se refiere a un sistema digital probabilístico inmune al ruido y a la radicación, que resulta especialmente ventajoso para la implementación de circuitos neuronales. Dicho sistema comprende una unidad aritmética basada en lógica estocástica extendida (ESL), configurada para realizar la suma de una pluralidad de señales de entrada, donde dicha unidad aritmética ESL comprende al menos dos señales de salida de dicha unidad: donde dichas señales de salida de la unidad aritmética ESL se encuentran conectadas a sendos conversores de señal estocástica a señal binaria P2B(N) de N ciclos que, a su vez, se encuentran conectados a comparadores binarios; y donde los comparadores binarios se encuentran conectados a un multiplexor que proporciona, al menos, dos señales probabilísticas de salida.

#### **DESCRIPCIÓN**

## SISTEMAS DIGITALES PROBABILÍSTICOS INMUNES AL RUIDO ELECTROMAGNÉTICO

5

10

15

20

25

30

#### **CAMPO DE LA INVENCIÓN**

La presente invención se enmarca en el campo de la electrónica digital. Más concretamente, la invención se refiere a sistemas digitales probabilísticos basados en lógica estocástica que poseen una alta inmunidad al ruido electromagnético.

#### ANTECEDENTES DE LA INVENCIÓN

En el estado de la técnica correspondiente al campo de la presente invención, es conocida la aplicación de la teoría de probabilidades a los circuitos digitales con el fin de implementar operaciones algebraicas de forma sencilla, comparada con la lógica digital tradicional. Por ejemplo, en la referencia [1] del presente documento se describe cómo, partiendo de señales digitales pulsantes aperiódicas, se pueden implementar operaciones aritméticas complejas como la suma o la multiplicación a partir de circuitos digitales sencillos. Estas propiedades pueden ser usadas para implementar cualquier función aritmética o para la realización de sistemas de inteligencia computacional como puede ser el reconocimiento de patrones o la minería de datos (también conocida como "big data").

La desventaja de esta forma de utilizar las puertas lógicas se presenta cuando se quiere almacenar o reconvertir la información de cada computación realizada en circuitos binarios. En cada canal estocástico de la información sobre la que se quiere determinar su actividad (y por tanto conocer el valor numérico que representa), se ha de integrar durante un tiempo suficiente el número de pulsos proporcionados por la señal correspondiente. Este hecho hace que, en caso de querer obtenerse suficiente precisión en las mediciones de dicha señal, el tiempo de computación necesario para obtener determinadas operaciones será mucho mayor que el usado por la tecnología digital clásica que se utiliza actualmente. Este hecho hizo abandonar dicha tecnología a mediados de la década de 1970, cuando surgieron los primeros microprocesadores basados en la lógica digital convencional y que proporcionaban altas precisiones con tiempos de computación menores.

35

Otra de las características diferenciadoras de este tipo de lógica es la necesidad de la descorrelación entre las señales que se operan. Esta descorrelación temporal de las señales es necesaria para poder implementar las operaciones aritméticas básicas. Hay que reseñar que, en los principios de la computación, la lógica estocástica se postulaba como una lógica alternativa a la lógica binaria booleana tradicional siendo, por tanto, su aplicación tan generalista como ésta. La principal razón de su entrada en desuso y olvido se debió a la falta de precisión en las operaciones que se realizaban (por su naturaleza probabilística) y debido, sobre todo, a la necesidad de usar sistemas deterministas de gran precisión para automatizar las actividades económico-financieras tanto en el ámbito doméstico como empresarial, que se correspondían con los principales sectores demandantes de sistemas de computación.

De esta forma, la computación estocástica o probabilística no se desarrolló durante los años siguientes. No obstante, este tipo de computación ha sido utilizada en los últimos años para la implementación de redes neuronales en hardware, tal y como se describe en las referencias [2-6] del presente documento.

A medida que la tecnología de integración de los circuitos ha evolucionado desde finales de la década de 1950 hasta la actualidad, se han incrementado exponencialmente el número de transistores que se pueden implementar en un solo circuito integrado. Según la conocida ley de Moore, cada dos años la tecnología dobla sus prestaciones. Esto implica, por ejemplo, que en un período de 20 años (desde principios de los 90 hasta la actualidad) la tecnología se haya multiplicado por un factor 1000 o más, permitiendo actualmente la integración de miles de millones de transistores en un solo circuito integrado. Mencionar también que, debido a que los circuitos digitales se suelen fabricar para que utilicen la lógica booleana tradicional y que dicha lógica, al ser determinista, requiere un 100% en la precisión de todos los procesos que se realicen en él, es necesario que los transistores que componen las puertas digitales tengan que tener también una alta fiabilidad. Este hecho hace que el escalado de los transistores no sea lo agresivo que podría ser si, por ejemplo, se tuviesen que implementar diseños digitales que operasen con algún tipo de lógica que fuese mucho más inmune al ruido que la lógica binaria tradicional.

Los altos niveles de integración que permite actualmente la tecnología hacen que, actualmente, se hayan abierto paso nuevas aplicaciones de alto nivel relacionadas con la inteligencia computacional como el reconocimiento de patrones (voz, facial, etc.) o la minería de datos (big data). Este nuevo escenario abre grandes posibilidades para el uso de

lógicas digitales no-deterministas, como la lógica estocástica o probabilística, en aplicaciones en donde se necesite gran paralelismo y no sea necesario conocer o almacenar los resultados parciales de la computación de cada módulo estocástico que esté operativo. Éste es el caso, por ejemplo, de los sistemas de reconocimiento de formas en donde a partir de una gran cantidad de información de entrada y de la realización probabilística de muchos procesos en paralelo, se determina si determinado estímulo complejo pertenece o no a una categoría concreta. En el caso de la exploración de grandes bases de datos (relacionado con aplicaciones de big-data) el proceso consiste en identificar el conjunto de vectores de la base de datos que mejor coincidan con el patrón modelo que se esté buscando. De esta forma, y gracias al reducido tamaño de las estructuras lógicas que requieren los elementos computacionales estocásticos o probabilísticos, se pueden incrementar considerablemente el número de estos bloques a la vez que la velocidad de proceso de éstos, posibilitando así la computación masiva en paralelo. Recientes trabajos [7] realzan este hecho y demuestran, por ejemplo, que para el caso concreto del reconocimiento de patrones, la lógica estocástica es varios órdenes de magnitud más rápida que la lógica tradicional basada en microprocesadores. Esto puede ser considerado, en este campo concreto, como una gran ventaja de esta tecnología con respecto a la lógica tradicional.

5

10

15

25

30

35

20 En cuanto a estudios del estado de la técnica relacionados con la aplicación de sistemas de inteligencia computacional mediante lógica estocástica, cabe citar los siguientes:

En el documento [8] se divulgan elementos de hardware para implementar sistemas basados en redes neuronales a partir de señales pulsantes. Se utilizan señales binarias pulsantes descorrelacionadas para la realización de comparaciones de forma rápida y eficiente. Un sistema similar se analiza también en la referencia [9].

En la referencia [10] se presenta una revisión sobre elementos de hardware eficientes para implementar redes neuronales que permiten generar vectores aleatorios, donde se muestra un prototipo de bajo coste que combina una puerta lógica XOR y un registro electrónico de N-bits.

En la referencia [11] se divulga una metodología probabilística de reconocimiento de patrones basada en comparaciones en paralelo. Se presenta un sistema digital que permite obtener la señal más próxima al patrón utilizando puertas lógicas y bloques comparadores.

#### ES 2 535 779 A1

Las señales pulsantes que se utilizan deben estar descorrelacionadas entre ellas para poder realizar las operaciones.

Recientemente se ha introducido una evolución muy relevante a la lógica estocástica tradicional. Dicha lógica se denomina lógica estocástica extendida (o, en su término inglés, "Extended Stochastic Logic", o "ESL") y está descrita en la referencia [12]. En dicha publicación se introduce este tipo de lógica (ESL) y se indica cómo implementar bloques aritméticos básicos (sumadores, divisores, multiplicadores, restadores) así como otros más complejos, tales como la implementación de la función tangente hiperbólica que se utiliza para la implementación de redes neuronales.

Finalmente, en la citada referencia [12] se especifica también cómo implementar una realización de un modelo neuronal mediante sistema digital probabilístico basado en lógica ESL. Sin embargo, el diseño propuesto en dicha referencia, que utiliza un divisor estocástico para la realización de la función de activación (en este caso una tangente hiperbólica), ralentiza considerablemente la función neuronal, lo que conlleva tiempos de respuesta excesivamente grandes para este tipo de aplicaciones.

La presente invención establece y explica las propiedades de inmunidad al ruido de la lógica ESL, no descritas hasta ahora, que suponen una notable mejora frente a los dispositivos del estado de la técnica basados en el uso de hardware evolutivo (EHW) y que toleran hasta un máximo de 35-40% de ruido (ver por ejemplo, en la referencia [13]). Asimismo, la invención presenta una forma más eficiente para la implementación de la función tangente hiperbólica mediante la lógica empleada. En la referencia [12], los autores utilizan un divisor estocástico realimentado que necesita del orden de 2<sup>24</sup> ciclos de reloj para estabilizarse. Esto hace que el bloque neuronal responda en segundos en el caso de utilizar relojes con frecuencias del orden de 10<sup>8</sup> Hz. La respuesta obtenida mediante el sistema de la presente invención mejora sustancialmente los tiempos de respuesta de este tipo de sistemas neuronales.

30

35

25

5

10

15

20

La presente invención plantea, pues, una solución a los problemas técnicos anteriormente referidos existentes en el estado de la técnica, mediante un novedoso circuito que elimina la dependencia del divisor estocástico y que mejora notablemente la respuesta del sistema neuronal propuesto en la referencia [12], presentando además inmunidad al efecto del ruido en las señales de salida. También se describe por primera vez la inmunidad al ruido electromagnético que proporciona la lógica ESL.

#### **REFERENCIAS**

5

25

30

- [1] B.R. Gaines, "Random pulse machines", IEEE Trans. on Comp. 410 (1968).

- [2] Y. Maeda, Y. Fukuda, "FPGA Implementation of Pulse Density Hopfield Neural Network", *Proc. Int. Joint Conf. on Neural Networks, Florida, USA*, (2007).

- [3] Y. Kondo, Y. Sawada, "Functional Abilities of a Stochastic Logic Neural Network",

10 IEEE Trans. on Neural Networks, 3 (3), 434-443 (1992).

- [4] S. Sato, K. Nemoto, S. Akimoto, M. Kinjo, K. Nakajima, "Implementation of a New Neurochip Using Stochastic Logic", *IEEE Trans. on Neural Networks, 14 (5), 1122-1127* (2003).

- [5] S.L. Bade, B. Hutchings. "FPGA-Based Stochastic Neural Networks Implementation", Proc. IEEE Workshop on FPGAs for Custom Computing Machines, Napa Valley, CA, USA, 189-198 (1994).

- [6] B. Brown, H. Card, "Stochastic Neural Computation I: Computational Elements" IEEE Transactions on Computers, Volume. 50, Issue. 9, 891–905 (2001)

- [7] V. Canals, A. Morro, J.L. Rosselló, "Stochastic-Based pattern-recognition analysis", *Pattern Recognition Letters 20101101, Elsevier* (2010)

- [8] J.L. Rosselló, V. Canals, A. Morro, "Hardware implementation of stochastic-based Neural Networks", Proceedings of the International Joint Conference on Neural Networks (2010), IEEE World Congress on Computational Intelligence, WCCI 2010 (2010), International Joint Conference on Neural Networks, IJCNN 2010 (2010).

- [9] "Hardware Implementation Of Stochastic Spiking Neural Networks", *International Journal of Neural Systems, vol.2, no.4*, (2012).

- [10] J.L. Rosselló, V. Canals, A. Morro, I. De Paul, "Practical hardware implementation of self-configuring neural networks", Lecture Notes in Computer

#### ES 2 535 779 A1

Science (Lecture Notes in Artificial Intelligence and Lecture Notes in Bioinformatics) - Advances in Neural Networks - ISNN 2009 - 6th International Symposium on Neural Networks, ISNN 2009, Proceedings (2009).

- [11] J.L. Roselló; V. Canals, I. De Paul, J. Segura, "Using stochastic logic for efficient pattern recognition analysis", Proceedings of the International Joint Conference on Neural Networks 2008 International Joint Conference on Neural Networks, IJCNN 2008 (2008).

- [12] J.L. Rosselló, V. Canals, A. Morro, "Probabilistic-based Neural Network Implementation", World Congress on Computational Intelligence 2012, Brisbane, Australia (2012).

- [13] M. Hartmann, P.C. Haddow, "Evolution of fault-tolerant and noise-robust digital designs," Computers and Digital Techniques, IEE Proceedings, vol. 151, no. 4, pp. 287-294 (2004).

#### DESCRIPCIÓN BREVE DE LA INVENCIÓN

20 Un objeto de la presente invención es obtener un sistema digital, adecuado para su aplicación a circuitos neuronales, que proporciona una respuesta mejorada frente a los sistemas del estado de la técnica.

Dicho objeto la invención se consigue mediante un sistema digital probabilístico que comprende, preferentemente:

- al menos, una unidad aritmética basada en lógica ESL, configurada para realizar la suma de una pluralidad de señales de entrada, ponderadas mediante una pluralidad de pesos estadísticos, donde dicha unidad aritmética ESL comprende al menos dos señales de salida de dicha unidad;

- donde dichas señales de salida de la unidad aritmética ESL se encuentran conectadas a sendos conversores de señal estocástica a señal binaria de tipo P2B(N) de N ciclos que, a su vez, se encuentran conectados a, al menos, tres comparadores binarios configurados para realizar una comparación de magnitud entre las señales binarias de salida de los dos conversores de señal P2B(N);

- y donde los comparadores binarios se encuentran conectados a un multiplexor que proporciona, al menos, dos señales probabilísticas de salida.

Se consigue con ello un sistema que sustituye el divisor utilizado en la referencia [12] por un multiplexor con el que se obtienen, ventajosamente, tiempos de respuesta notablemente más cortos que con el circuito descrito en dicha referencia.

Preferentemente, la respuesta que se obtiene a la salida del sistema digital probabilístico según la realización anteriormente descrita, con respecto a sus entradas, corresponde a dos señales, donde al menos una de dichas señales posee una salida con función de respuesta de tangente hiperbólica. Se consigue con ello una respuesta adecuada para su uso en la implementación de circuitos neuronales probabilísticos individuales y/o redes neuronales de circuitos.

15

20

25

30

35

La presente invención describe, asimismo, cómo determinados sistemas digitales probabilísticos (la lógica ESL, que será explicada en mayor detalle más adelante en el presente documento) son adecuados para ejecutar con gran fiabilidad tareas aritméticas complejas en entornos con altos niveles de ruido. Los sistemas digitales tradicionales presentan problemas de fiabilidad en entornos con altos niveles de radiación o ruido electromagnético de forma que, por ejemplo, el cambio de un solo bit puede acarrear el malfuncionamiento global del sistema. La presente invención presenta una solución robusta e inmune al ruido para la implementación de sistemas digitales en entornos hostiles (aplicaciones espaciales, en emplazamientos nucleares que presenten altos niveles de radiación o en aplicaciones militares como contramedidas a la guerra electrónica). Cabe destacar que los circuitos digitales actuales se fabrican con altos criterios de robustez para que sean lo más inmunes al ruido, teniendo en cuenta que con ellos normalmente se implementan funcionalidades de lógica binaria. Si se sustituye dicha lógica binaria por la lógica probabilística ESL, entonces dicha robustez no tiene tanto sentido, puesto que dicha lógica ESL presenta una inmunidad al ruido prácticamente total. Por tanto, el hecho de substituir la lógica binaria booleana por la probabilística ESL para la implementación de sistemas aritméticos digitales implicaría el poder fabricar puertas lógicas con transistores mucho más pequeños, con el consiguiente aumento en la complejidad que se pueda finalmente implementar. Lo que se describe, por tanto, en la presente invención es una nueva funcionalidad de la lógica ESL para la implementación de sistemas prácticamente inmunes al ruido que implica tanto una solución para los sistemas digitales que tienen que operar en entornos hostiles de alta radiación (espaciales, militares, etc.), siendo ventajosa también a la hora de reducir el tamaño de los transistores que constituyen las puertas digitales, con el consiguiente aumento de las capacidades de los circuitos construidos.

#### ES 2 535 779 A1

Según las ventajas anteriores, otro aspecto de la invención se refiere, pues, al uso de cualquier sistema basado en lógica ESL para atenuar el efecto del ruido en un circuito, y más preferentemente de un sistema según cualquiera de las realizaciones descritas en el presente documento.

5

10

Adicionalmente, otro aspecto de la invención se refiere a un método de protección contra el efecto del ruido en circuitos, que comprende la aplicación de un sistema de lógica digital ESL a al menos una de las salidas de dichos circuitos. Preferentemente, dicho método comprende la aplicación de un sistema según cualquiera de las realizaciones descritas en el presente documento.

#### **DESCRIPCIÓN DE LOS DIBUJOS**

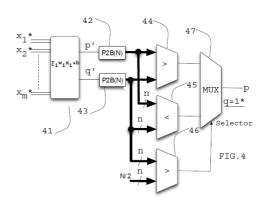

La Figura 1 muestra cómo dos señales  $x^*$  e  $y^*$ , representadas por las señales  $p_x$ ,  $q_x$ ,  $p_y$   $q_y$ ; se tienen que operar mediante lógica ESL para realizar el producto y la división ( $x^*y^*$   $x^*/y^*$  que están representadas por las señales  $p_{xy}$   $q_{xy}$  e  $p_{x/y}$   $q_{x/y}$ , respectivamente), mediante el uso de dos puertas lógicas XNOR.

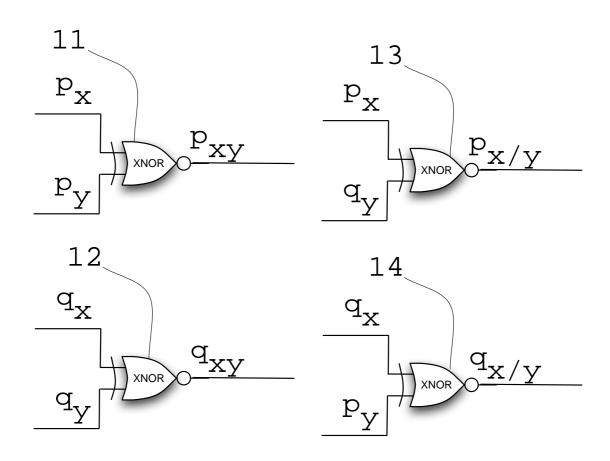

La Figura 2 muestra cómo dos señales  $\mathbf{x}^*$  e  $\mathbf{y}^*$ , representadas por los bits  $p_x$ ,  $q_x$ ,  $p_y$ ,  $q_y$ , se tienen que operar mediante lógica ESL para realizar una suma (x+y) con la lógica ESL, mediante la aplicación de dos multiplexores, junto con puertas XNOR.

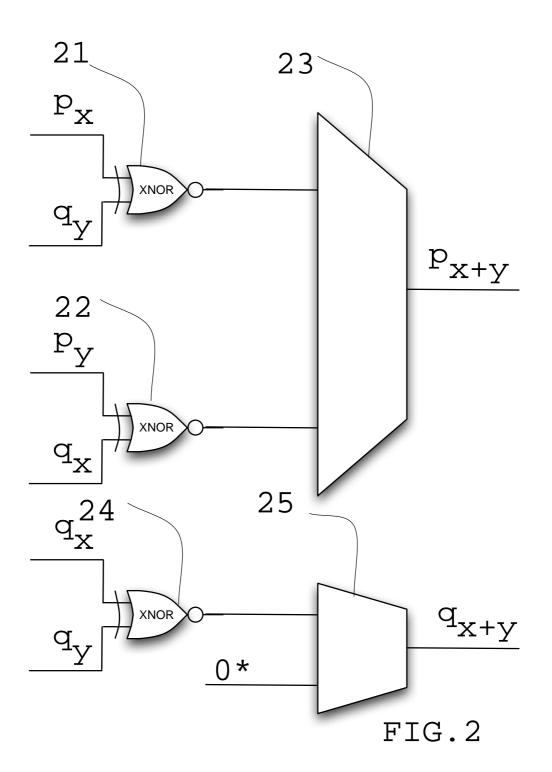

La Figura 3 muestra cómo dos señales  $\mathbf{x}^*$  e  $\mathbf{y}^*$ , representadas por los bits  $p_x$ ,  $q_x$ ,  $p_y$   $q_y$ , se tienen que operar mediante lógica ESL para realizar una resta (x-y) con la lógica ESL, mediante la aplicación de dos multiplexores y con puertas XNOR, junto con un inversor situado a continuación de una de las puertas XNOR.

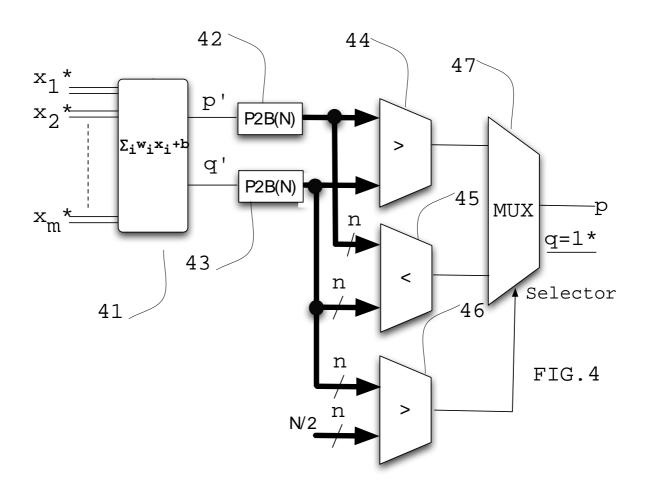

La Figura 4 muestra una implementación de un sistema digital probabilístico ESL mejorado, aplicado a un modelo neuronal, según una realización preferente de la invención.

30

25

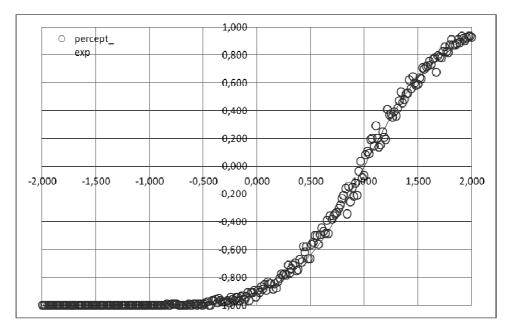

La Figura 5 muestra los resultados experimentales del funcionamiento del sistema mostrado en la Figura 4, según una realización preferente de la invención.

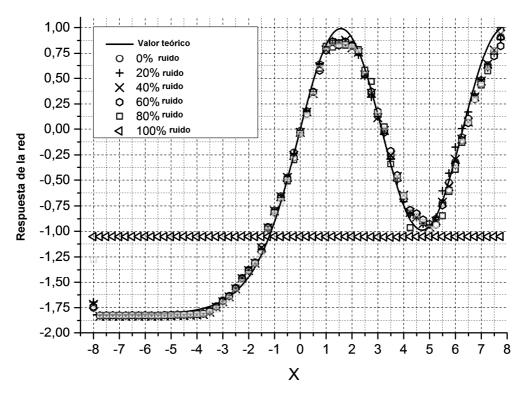

La Figura 6 muestra la respuesta de la red neuronal ESL cuando es sometida a diferentes niveles de ruido (desde un 0% hasta un 100% en el eje x) y en donde se muestra gráficamente la inmunidad al ruido de dicha lógica.

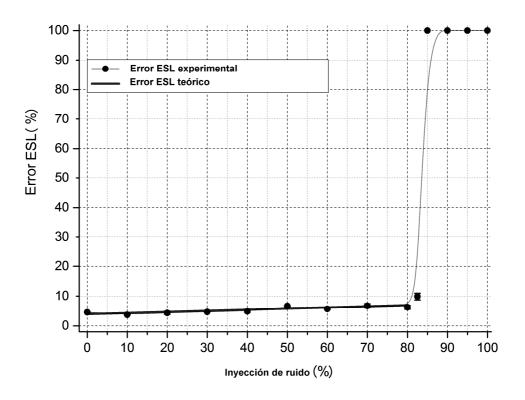

La Figura 7 muestra una representación del porcentaje de error con respecto al ruido inyectado en un sistema según una realización preferente de la presente invención.

#### DESCRIPCIÓN DETALLADA DE LA INVENCIÓN

5

10

Para la mejor comprensión de las realizaciones preferentes de la invención, se explicarán a continuación los principios básicos de la lógica estocástica extendida (conocida como "Extended Stochastic Logic" en inglés, o "ESL"), así como sus funciones aritméticas básicas. Después, se describirá una realización de la invención relativa a su aplicación a un circuito neuronal y, finalmente, se explicará y demostrará la principal funcionalidad de la lógica ESL, que es su gran inmunidad al ruido, hecho que no es compartido por la lógica estocástica tradicional y que es un distintivo único de dicha lógica ESL.

#### La codificación ESL:

15

La lógica estocástica es el resultado de la aplicación de las leyes de la probabilidad a la lógica digital, en donde las variables son representadas mediante señales pulsantes estocásticas que poseen una probabilidad de activación determinada (p). Dicha probabilidad de activación está definida, pues, entre 0 y 1 (en adelante se hablarán de probabilidades de activación con variables en minúscula y sin asterisco, como las probabilidades p y q).

25

20

Por su parte, la lógica ESL consiste en la codificación temporal de señales mediante pares de bits pulsantes. La señal que codifica cada par de bits (**x**\*) está relacionada con la frecuencia de activación de dichos bits mediante la fórmula

$$x^* = \frac{p^*}{q^*} = \frac{2p-1}{2q-1} \tag{1}$$

en donde p y q son las probabilidades de activación de los dos bits ( $p^*$  y  $q^*$  son cambios de variables de probabilidades a señales de actividad). Las tramas de bits de ambas señales no siguen ningún patrón predeterminado, con lo que se posibilita el poder operar con señales pulsantes usando las leyes de la probabilidad.

#### La aritmética ESL:

35

30

La lógica ESL presenta una aritmética particular que permite el llevar a cabo prácticamente cualquier función aritmética. Se explica a continuación cómo realizar la suma, resta, multiplicación y división bajo dicha lógica.

La multiplicación y la división se realizan mediante la aplicación de dos puertas XNOR a las tramas de señales. En la Figura 1 se muestra cómo dos señales ESL  $\mathbf{x}^*$  e  $\mathbf{y}^*$ , representadas por las señales  $p_x$ ,  $q_x$ ,  $p_y$ ,  $q_y$ ; se tienen que operar para realizar el producto y la división ( $\mathbf{x}^*\mathbf{y}^*$   $\mathbf{x}^*/\mathbf{y}^*$  que estarán representadas por las señales  $p_{xy}$ ,  $q_{xy}$  y  $p_{x/y}$ ,  $q_{x/y}$ , respectivamente). Para ello, se utilizan dos puertas lógicas XNOR para la multiplicación (11) y (12) así como otras dos puertas lógicas XNOR para realizar la división (13) y (14).

En las Figuras 2 y 3 se muestra cómo dos señales ESL  $x^*$  e  $y^*$ , representadas ambas por los bits  $p_x$ ,  $q_x$ ,  $p_y$ ,  $q_y$ , se tienen que operar para realizar la suma y la resta (x+y, x-y). En la Figura 2 se muestra cómo se puede realizar una suma con la lógica ESL mediante la aplicación de dos multiplexores (23) y (25) junto con puertas XNOR (21, 22, 24). Una de las entradas del multiplexor (25) se conecta a una señal pulsante de valor  $0^*$  (equivalente a una señal que tiene un 50% de probabilidades de ser '1' o '0'). Para el caso de la implementación de una resta (Figura 3), el esquema es idéntico pero insertando un inversor después de la puerta XNOR (32).

En la referencia [12] se explican con mayor detalle las citadas implementaciones aritméticas de la lógica ESL.

20

25

5

10

15

#### Aplicación a la implementación de un sistema neuronal basado en lógica digital ESL:

En la Figura 4 se muestra una implementación de un sistema digital probabilístico ESL mejorado, aplicado a un modelo neuronal según una realización preferente de la invención. Dicho sistema comprende, al menos, una unidad aritmética ESL (41) configurada para realizar la suma de una pluralidad de señales de entrada  $\mathbf{x}^*_i$ , ponderadas mediante una pluralidad de pesos  $\mathbf{w}_i$ , donde dicha unidad aritmética ESL (41) comprende al menos dos señales de salida p' y q' de dicha unidad.

30 Las señales de salida p' y q' de la unidad aritmética ESL (41) se encuentran conectadas a sendos conversores de señal estocástica a señal binaria P2B(N) (42, 43) que, a su vez, se encuentran conectados a, al menos, tres comparadores binarios (44, 45, 46) configurados para realizar una comparación de magnitud entre las señales binarias de salida de los dos conversores de señal P2B(N) (42, 43). Por su parte, dichos comparadores binarios (44, 45, 46) se encuentran conectados a un multiplexor (47) que proporciona, al menos, dos señales probabilísticas de salida p y q.

Los conversores de señal P2B(N) (42, 43) están ampliamente descritos en el estado de la técnica constituido por las referencias del presente documento, y consisten en contadores que proporcionan señales binarias de salida configuradas como el número de veces que las señales estocásticas a convertir p' y q' son iguales a '1', durante N ciclos.

5

10

15

20

Por otra parte, los comparadores binarios (44, 45, 46) están configurados para comparar las señales p' y q' y comprobar si p'>q' o de si p'<q' en caso de que q'<0. Esto es lo mismo que comprobar si p'/q'>1. Para saber si q'<0, lo que se hace es comparar la salida de uno de los conversores P2B(N) (43) con N/2 (que definiría el cero). N es el número de ciclos durante los cuales se hace el conteo de "unos" proporcionado por las señales p' y q'. Si los dos conversores P2B(N) proporcionaran a su salida el valor exacto de las señales de entrada p' y q', entonces a la salida del comparador se obtendría una función escalón entre +1 (si p'/q'>1) y -1 (si p'/q'<1). Pero los dos conversores no proporcionan el valor exacto de la actividad de sus salidas (al ser N un número finito). Como consecuencia, se produce una salida correspondiente a una función escalón suavizada, en relación directa con el valor de N (más suave a medida que N disminuye).

La respuesta que se obtiene a la salida del sistema digital probabilístico según la realización anteriormente descrita, con respecto a las entradas  $\mathbf{x}^*_i$ , corresponde a dos señales p y q de una neurona con función de activación de tangente hiperbólica. En una realización preferente de la invención, la señal q de salida se fija a un '1' lógico (probabilidad de activación del 100%) y la señal de salida ESL p viene dada por:

Salida ESL =

$$\frac{2p-1}{2q-1} = f\left(\sum_{i=1}^{m} w_i x_i^* + b - 1\right)$$

(2)

25

donde la función f es la función tangente hiperbólica f(x)=tanh(x) y b es una cantidad constante.

En la Figura 5 se muestran los resultados experimentales del funcionamiento del sistema de circuito mostrado en la Figura 4 cuando m=1 (una única señal), w=1 y b=0. En este caso, la salida de la neurona es la tangente hiperbólica. Como se puede observar, los resultados experimentales obtenidos (círculos) replican la función buscada (línea sólida) con una

#### 35 Inmunidad al ruido de la lógica ESL:

buena precisión.

#### ES 2 535 779 A1

La ventaja característica más importante de la lógica ESL en este tipo de sistemas es su práctica inmunidad al ruido. Dicha propiedad no ha sido descrita con anterioridad en ninguno los estudios anteriores del estado de la técnica.

Cuando el ruido varía una señal digital más allá de su valor esperado, puede suponer un gran problema para un sistema digital basado en lógica booleana, puesto que una simple inversión de un bit puede significar el bloqueo del sistema completo. La realización del circuito neuronal de la Figura 4 sirve para mostrar cómo la lógica ESL presenta una práctica inmunidad al ruido, puesto que la división de dos señales estocásticas (p\*/q\*) que están afectadas por los mismos niveles de ruido (que implica la inversión de las señales p y q en instantes de tiempo indeterminados) se mantiene constante. Dicha relación (p\*/q\*) es compartida por cualquier sistema basado en este tipo de lógica, lo que permite establecer la idoneidad de los sistemas ESL como medio de atenuación o de impermeabilización frente al ruido electromagnético.

Si bien una señal estará expuesta al mismo nivel de ruido que la otra, dicha exposición puede afectar a ambas señales en instantes diferentes. Una señal estocástica p\* que es invertida con una determinada frecuencia r variará su valor al producto -p\*r\*. (r\*=2r-1). Si dos señales estocásticas p\* y q\* se ven afectadas en la misma medida por una señal de ruido, variarán por tanto sus valores a -p\*r\* y a -q\*r\*, manteniendo invariante su relación p\*r\*/q\*r\*=p\*/q\*. Por tanto, la magnitud codificada se mantendrá constante independientemente de los efectos del ruido electromagnético o de la radiación.

Para probar la robustez de la lógica ESL según la presente invención, se inyectan diferentes niveles de ruido a la entrada de un bloque ESL determinado y se observa su salida. Concretamente, se utiliza una red neuronal compuesta por neuronas (cada una descrita por la Figura 4, aunque siendo extrapolable a cualquier otro sistema ESL) y que realiza el ajuste de una función seno en el intervalo cerrado [0,7]. Para simular el ruido externo, se imponen cambios aleatorios a las señales de salida del sistema p y q en instantes de tiempo diferentes. Se define el ruido máximo posible (100%) como aquel que hace que se pierda completamente la información de la señal. En esta situación, existen tantos cambios de señal debido al ruido externo, que la probabilidad de tener un '0' o un '1' en cualquier momento se hace del 50%. Esta situación se corresponde con los valores p\*=q\*=0, y por tanto x\*=0/0, implicando una pérdida de la señal estocástica.

Al a vez que se inyecta ruido entre un 0% y un 100%, se evalúa el error cometido por la red neuronal ESL, comparando el comportamiento de la red con el comportamiento esperado teórico.

5

10

$$Error(\%\_ruido) = \frac{\frac{1}{n} \cdot \sum_{i=1}^{n} abs(f_{NN}(ruido) - f_{NN}(teoria))}{\sqrt{\frac{1}{n} \cdot \sum_{i=1}^{n} (f_{NN}(teoria)^{2})}}$$

(3)

Los resultados se muestran en las Figuras 6 y 7. En la Figura 6 se muestra la respuesta de la red neuronal ESL cuando es sometida a diferentes niveles de ruido (desde un 0% hasta un 100%). Se puede apreciar cómo el comportamiento es prácticamente el mismo independientemente del ruido para niveles comparables o inferiores a un 80%. Este efecto se aprecia mejor en la Figura 7, donde se representa el error (usando la ecuación (3) anterior) con respecto al ruido inyectado. En dicha figura se aprecia que la red neuronal ESL presenta inmunidad al ruido en niveles comparables o inferiores al 80%.

Los resultados medidos descritos en los párrafos precedentes demuestran, en consecuencia, la inmunidad al ruido de la tecnología ESL. Dicha inmunidad no había sido descrita anteriormente. Los niveles de inmunidad obtenidos se pueden comparar a los niveles conseguidos por otros sistemas digitales del estado de la técnica (que toleran hasta un máximo de 35-40% de ruido), comprobándose que la presente invención supone una considerable mejora sobre los mismos.

#### **REIVINDICACIONES**

1.- Uso de un sistema electrónico de lógica digital ESL como medio de atenuación del ruido electromagnético.

5

10

15

25

30

35

2.- Uso según la reivindicación anterior, donde el sistema electrónico incluye un circuito digital probabilístico que comprende los siguientes elementos:

al menos, una unidad aritmética ESL (41) configurada para realizar la suma de una pluralidad de señales de entrada  $x^*_i$ , ponderadas mediante una pluralidad de pesos estadísticos  $w_i$ , donde dicha unidad aritmética ESL (41) comprende al menos dos señales de salida p' y q' de dicha unidad;

donde dichas señales de salida p' y q' de la unidad aritmética ESL (41) se encuentran conectadas a sendos conversores de señal estocástica a señal binaria P2B(N) (42, 43) de N ciclos que, a su vez, se encuentran conectados a, al menos, tres comparadores binarios (44, 45, 46) configurados para realizar una comparación de magnitud entre las señales binarias de salida de los conversores de señal P2B(N) (42, 43);

y donde los comparadores binarios (44, 45, 46) se encuentran conectados a un multiplexor (47) que proporciona, al menos, dos señales probabilísticas de salida p y q.

- 20 3.- Uso según cualquiera de las reivindicaciones anteriores en un entorno en presencia de radiación electromagnética.

- 4.- Sistema digital probabilístico que comprende los siguientes elementos:

al menos, una unidad aritmética ESL (41) configurada para realizar la suma de una pluralidad de señales de entrada  $x^*_i$ , ponderadas mediante una pluralidad de pesos estadísticos  $w_i$ , donde dicha unidad aritmética ESL (41) comprende al menos dos señales de salida p' y q' de dicha unidad;

donde dichas señales de salida p' y q' de la unidad aritmética ESL (41) se encuentran conectadas a sendos conversores de señal estocástica a señal binaria P2B(N) (42, 43) de N ciclos que, a su vez, se encuentran conectados a, al menos, tres comparadores binarios (44, 45, 46) configurados para realizar una comparación de magnitud entre las señales binarias de salida de los conversores de señal P2B(N) (42, 43);

y caracterizado por que los comparadores binarios (44, 45, 46) se encuentran conectados a un multiplexor (47) que proporciona, al menos, dos señales probabilísticas de salida p y q.

- 5.- Sistema según la reivindicación anterior, donde los comparadores binarios (44, 45, 46) están configurados para comparar las señales p' y q' y comprobar si p'>q' o de si p'<q' en caso de que q'<0.

- 6.- Sistema según cualquiera de las reivindicaciones 4-5, donde al menos uno de los comparadores binarios (46) está configurado para comparar la señal binaria de salida de uno de los conversores P2B(N) (43) con una señal de entrada en dicho comparador binario (43) de valor N/2.

- 7.- Sistema según cualquiera de las reivindicaciones 4-6, donde la respuesta que se obtiene a la salida del sistema digital probabilístico según la realización anteriormente descrita, con respecto a las entradas x\*i, corresponde a dos señales ESL p y q, donde al menos una de dichas señales posee una función de respuesta de tangente hiperbólica.

- 8.- Sistema según la reivindicación anterior, donde una de las señales de salida (q) se fija a un '1' lógico y donde la otra señal de salida (p) viene dada por la función f:

$$Salida\ ESL = f\left(\sum_{i=1}^{m} w_i x_i^* + b - 1\right)$$

donde la función f es la función tangente hiperbólica f(x)=tanh(x) y b es una cantidad constante.

20

30

- 9.- Circuito neuronal probabilístico que comprende un sistema según cualquiera de las reivindicaciones 4-8.

- 10.- Método de protección contra el efecto del ruido electromagnético en circuitos

25 que comprende la aplicación de un sistema electrónico de lógica digital ESL a, al menos, una de las salidas de dichos circuitos.

- 11.- Método según la reivindicación anterior, que comprende la aplicación de un sistema según cualquiera de las reivindicaciones 4-8 a, al menos, una de las salidas de dichos circuitos.

FIG.1

FIG. 5

FIG. 6

**FIG. 7**

(21) N.º solicitud: 201331656

2 Fecha de presentación de la solicitud: 14.11.2013

32 Fecha de prioridad:

#### INFORME SOBRE EL ESTADO DE LA TECNICA

| ⑤ Int. Cl.: | <b>G06F7/70</b> (2006.01) |

|-------------|---------------------------|

|             |                           |

#### **DOCUMENTOS RELEVANTES**

| Categoría                         | <b>66</b>                                | Documentos citados                                                                                                                                         | Reivindicaciones afectadas |

|-----------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| А                                 |                                          | abilistic-based neural network implementation," The 2012<br>Neural Networks (IJCNN), pp. 1,7, 10.06.2012.                                                  | 1-11                       |

| А                                 |                                          | en hardware de sistemas de alta fiabilidad basados en s doctoral. Departamento de Física. Universitat de les Illes s 2.2.5, 2.2.6, 4.3.2.2.2 y 4.3.2.4.2.  | 1-11                       |

| А                                 |                                          | cuits for probabilistic computation in the presence of noise" ation Conference, 2005, pp. 485,490, 13.06.2005. Resumen.                                    | 1-11                       |

| Α                                 |                                          | n the stochastic computation using the ratio of one pulses and nal Symposium on Circuits and Systems, ISCAS '94, vol. 6, documento.                        | 1-11                       |

| Α                                 |                                          | hancement in stochastic pulse code systems using parallelism f the 23rd European Solid-State Circuits Conference, 1997. 1997. Apartados 2 y 5.             | 1-11                       |

| A                                 | Computing and Control Application        | Approximate Data Representation for Signal Processing, Soft tions". IEEE International Symposium on Intelligent Signal 1-6. 03.10.2007. Apartados II y IV. | 1-11                       |

| Cat<br>X: d<br>Y: d<br>r<br>A: re | resentación<br>de la fecha               |                                                                                                                                                            |                            |

|                                   | para todas las reivindicaciones          | para las reivindicaciones nº:                                                                                                                              |                            |

| Fecha                             | de realización del informe<br>14.01.2015 | Examinador<br>J. Cotillas Castellano                                                                                                                       | <b>Página</b><br>1/5       |

# INFORME DEL ESTADO DE LA TÉCNICA Nº de solicitud: 201331656 Documentación mínima buscada (sistema de clasificación seguido de los símbolos de clasificación) H03K, G06F Bases de datos electrónicas consultadas durante la búsqueda (nombre de la base de datos y, si es posible, términos de búsqueda utilizados) INVENES, EPODOC

**OPINIÓN ESCRITA**

Nº de solicitud: 201331656

Fecha de Realización de la Opinión Escrita: 14.01.2015

examen formal y técnico de la solicitud (Artículo 31.2 Ley 11/1986).

Declaración

Novedad (Art. 6.1 LP 11/1986)

Reivindicaciones 1-11

Reivindicaciones NO

Actividad inventiva (Art. 8.1 LP11/1986)

Reivindicaciones 1-11

Reivindicaciones NO

Se considera que la solicitud cumple con el requisito de aplicación industrial. Este requisito fue evaluado durante la fase de

#### Base de la Opinión.-

La presente opinión se ha realizado sobre la base de la solicitud de patente tal y como se publica.

Nº de solicitud: 201331656

#### 1. Documentos considerados.-

A continuación se relacionan los documentos pertenecientes al estado de la técnica tomados en consideración para la realización de esta opinión.

| Documento | Número Publicación o Identificación                                                                                                                                                                                                                    | Fecha Publicación |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| D01       | ROSSELLO, J.L. et al. "Probabilistic-based neural network implementation," The 2012 International Joint Conference on Neural Networks (IJCNN), pp. 1,7, 10.06.2012. Apartados II a V.                                                                  | 10.06.2012        |

| D02       | CANALS V.J. "Implementación en hardware de sistemas de alta fiabilidad basados en metodologías estocásticas". Tesis doctoral. Departamento de Física. Universitat de les Illes Balears. Mayo de 2012. Apartados 2.2.5, 2.2.6, 4.3.2.2.2 y 4.3.2.4.2.   | 01.05.2012        |

| D03       | NEPAL, K. "Designing logic circuits for probabilistic computation in the presence of noise" Proceedings. 42nd Design Automation Conference, 2005, pp. 485,490, 13.06.2005. Resumen.                                                                    | 13.06.2005        |

| D04       | SEUNG-JAI MIN et al. "A study on the stochastic computation using the ratio of one pulses and zero pulses," 1994 IEEE International Symposium on Circuits and Systems, ISCAS '94, vol. 6, pp. 471-474. 30.05.1994. Todo el documento.                  | 30.05.1994        |

| D05       | NAESS, S. et al. "Performance enhancement in stochastic pulse code systems using parallelism and redundancy". Proceedings of the 23rd European Solid-State Circuits Conference, 1997. ESSCIRC '97. pp. 400-403, 16.09.1997. Apartados 2 y 5.           | 16.09.1997        |

| D06       | PETRIU, E.M. "Biology Inspired Approximate Data Representation for Signal Processing, Soft Computing and Control Applications". IEEE International Symposium on Intelligent Signal Processing, 2007. WISP 2007. pp 1-6. 03.10.2007. Apartados II y IV. | 03.10.2007        |

### 2. Declaración motivada según los artículos 29.6 y 29.7 del Reglamento de ejecución de la Ley 11/1986, de 20 de marzo, de Patentes sobre la novedad y la actividad inventiva; citas y explicaciones en apoyo de esta declaración

Los documentos recuperados en la fase de búsqueda y citados en el Informe sobre el Estado de la Técnica, referidos a sistemas digitales probabilísticos, si bien presentan algunas similitudes con el sistema, uso, y métodos reivindicados, se diferencian en algunas características que hacen que el objeto de la solicitud se considere nuevo y con actividad inventiva, según lo establecido en los Art. 6.1 y 8.1 de LP.

#### Reivindicación independiente 1:

Los documentos D01 y D02 divulgan los sistemas electrónicos de lógica digital denominados ESL (Extended Stochastic Logic). Dicha lógica digital se basa en la representación de una señal mediante la razón de otras dos señales estocásticas (véanse el apartado II del documento D01, el apartado 2.2.5 del documento D02 o las líneas 15 a 31 de la página 10 de la descripción).

El documento D04 divulga un sistema digital estocástico en el que se utiliza la razón de dos variables estocásticas, si bien en este caso el numerador se hace corresponder al número de unos contados durante un tiempo de evaluación, mientras que el denominador sería el número de ceros.

Es conocido que los sistemas digitales probabilísticos en general ofrecen una inmunidad frente al ruido mayor que los sistemas lógicos determinísticos, como puede verse en los documentos D03, D05 o D06. Sin embargo, no se considera que resulte evidente para un experto en la materia la utilización de un sistema electrónico estocástico con una codificación del tipo ESL (descrita en D01 y D02) como medio de atenuación del ruido electromagnético, dado que la superior inmunidad al ruido de este tipo de sistemas es consecuencia directa de dicha codificación, y no de la utilización de un sistema probabilístico.

Por lo tanto, la reivindicación 1 cumpliría con los requisitos de novedad y actividad inventiva a la vista del Estado de la Técnica (Arts. 6.1 y 8.1 LP)

**OPINIÓN ESCRITA**

Nº de solicitud: 201331656

#### Reivindicación independiente 4:

El documento D02 describe un sistema digital probabilístico que comprende (véanse los apartados 4.3.2.2.2 en la página 393 y 4.3.2.4.2 en la página 402):

- Una unidad aritmética ESL que realiza la suma de una serie de señales de entrada ponderadas mediante unos pesos estadísticos que comprende dos señales de salida (véase la figura 4-42);

- Donde dichas señales de salida se conectan a sendos conversores de señal estocástica a señal binaria, cuyas salidas se conectan a las entradas de dos comparadores. La salida de los comparadores se conecta a una puerta XNOR.

Otro de los circuitos descritos en D02 comprende (véase la figura 4-47) una unidad aritmética ESL cuyas salidas se conectan a un divisor estocástico conectado a su vez a un bloque pseudo tangente hiperbólica.

Ni el documento D01 ni el D02 describen la utilización de tres comparadores conectados a la salida de los dos bloques conversores P2B y conectados a su vez a un multiplexor.

De este modo, en ninguno de los documentos citados se ha encontrado un circuito digital probabilístico con todas las características técnicas que se definen en la reivindicación independiente 4 de la solicitud. Asimismo, se considera que las características diferenciales no parecen derivarse de una manera evidente de ninguno de los documentos citados ni de manera individual ni mediante una combinación evidente entre ellos, por lo que la reivindicación 4 también sería nueva y supondría una actividad inventiva a la vista del Estado de la Técnica (Arts. 6.1 y 8.1 LP).

#### Reivindicaciones 2, 3, 5-11:

Por todo la anterior, se concluye que las reivindicaciones independientes 1 y 4, y por consiguiente, todas sus dependientes (reivindicaciones 2 y 3 respecto al uso, y reivindicaciones 5 a 8 respecto al sistema), así como las reivindicaciones 9 a 11, referidas a un circuito neuronal probabilístico que comprende el sistema de la reivindicación 4, y a un método de protección contra el ruido electromagnético mediante un sistema ESL, satisfarían los requisitos de patentabilidad establecidos en el Art. 4.1 de la Ley 11/1986 de Patentes.