# OFICINA ESPAÑOLA DE PATENTES Y MARCAS

ESPAÑA

11 Número de publicación: 2 478 791

21 Número de solicitud: 201330067

51 Int. Cl.:

H03K 17/687 (2006.01)

(12)

#### SOLICITUD DE PATENTE

Α1

(22) Fecha de presentación:

22.01.2013

(43) Fecha de publicación de la solicitud:

22.07.2014

(71) Solicitantes:

UNIVERSITAT DE LES ILLES BALEARS (100.0%) Campus Universitario. Ctra. de Valldemossa, Km.7,5. Edifici Son Lledo 07071 Palma de Mallorca (Illes Balears) ES

(72) Inventor/es:

CAMARERO DE LA ROSA, David; LAGZIRI, Manal; GARCÍA MORENO, Eugeni y PICOS GAYÁ, Rodrigo

(74) Agente/Representante:

**TEMIÑO CENICEROS, Ignacio**

54 Título: Interruptor con resistencia modificable

(57) Resumen:

Interruptor con resistencia modificable que comprende al menos un transistor (BT) con una resistencia equivalente en estado cerrado entre terminales ( $r_{on}$ ), y conectado con un circuito (BC) donde la resistencia entre terminales ( $r_{on}$ ) es proporcional a una tensión de entrada V <sub>cal</sub> del circuito BC.

# INTERRUPTOR CON RESISTENCIA MODIFICABLE

#### **DESCRIPCIÓN**

La presente invención describe un interruptor con resistencia modificable. En concreto un interruptor linealizado integrado en tecnología CMOS estándar con resistencia en estado cerrado que se puede modificar mediante una señal de calibración externa.

# ESTADO DE LA TÉCNICA

10

15

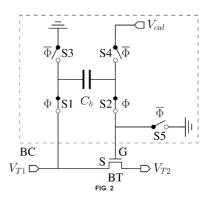

Se conoce en el estado de la técnica el artículo de [Dessouky, M.; Kaiser, A.; "Input switch configuration suitable for rail-to-rail operation of switched op amp circuits" Electronics Letters, vol.35, no.1, pp.8-10, 7 Jan 1999] que se puede considerar como el antecedente más cercano de la presente invención. En este artículo se desarrolla una versión de la técnica "gate-source bootstrap". No obstante, este documento no describe la posibilidad de ajustar las características eléctricas de un interruptor y, por tanto, no es posible su empleo en la calibración del ancho de banda de los circuitos de muestreo RC que se encuentran a la entrada de los convertidores analógico – digitales basados en entrelazamiento temporal (TI ADC en sus siglas en inglés). En la FIG. 1 se muestra el circuito propuesto en este documento.

20

25

Otro artículo importante del que se parte para el desarrollo de la presente invención es [Sai-Weng Sin et al. "Statistical Spectra of Distortion Analysis of Time-Interleaved Sampling Bandwidth Mismatch" IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, VOL. 55, NO. 7, JULY 2008]. En este artículo se cuantifica la pérdida de linealidad en convertidores analógico-digitales basados en entrelazamiento temporal (time-interleaved) debido a la disparidad del ancho de banda (bandwidth mismatch) de los interruptores de muestreo (sampling switches).

30

35

Del estado de la técnica se conoce también la patente estadounidense US7492207. En ella se emplea un circuito de "bootstrapping" y se implementan en él una serie de mejoras gracias a la introducción como señal a la puerta del transistor de una tensión predeterminada, seleccionada entre un número limitado de valores. Los problemas que soluciona dicha patente son la fiabilidad del circuito (esperanza de vida), la dependencia del "threshold voltage" con la señal de entrada y la dependencia de la tensión de "clock-

feedthrough" con la señal de entrada.

#### EXPLICACIÓN DE LA INVENCIÓN

10

15

20

25

30

35

La presente invención describe un interruptor con resistencia modificable. En concreto se trata de un interruptor linealizado cuya resistencia a la corriente eléctrica en estado cerrado puede ser modificable a voluntad mediante una señal de calibración externa.

La aplicación más importante de la presente invención es la calibración del ancho de banda de cada uno de los circuitos de muestreo de RC que se encuentran a la entrada de los convertidores analógico-digital basados en entrelazamiento temporal (TI ADC). Esta invención permite solucionar el problema técnico de implementación práctica de los TI ADC, relacionado con las variaciones aleatorias durante el proceso de fabricación del ancho de banda de los circuitos de muestreo RC. Esto es una gran ventaja ya que la disparidad en el ancho de banda de los circuitos de muestreo RC puede limitar la linealidad con la que un TI ADC es capaz de digitalizar señales analógicas.

Más concretamente, el interruptor con resistencia modificable comprende al menos un transistor con una resistencia equivalente en estado cerrado entre terminales conectado con un circuito que tiene una tensión de entrada variable y que comprende una pluralidad de interruptores conectados con una tensión de interrupción que abre y cierra dichos interruptores; y donde los citados interruptores están conectados en un puente en H; y que además comprende una capacidad conectada en paralelo entre ambas ramas del puente y donde de su estructura se infiere que la resistencia equivalente en estado cerrado entre terminales es proporcional a la tensión de entrada variable del circuito.

En un segundo aspecto de la invención, el circuito de muestreo comprende el interruptor descrito.

A lo largo de la descripción y las reivindicaciones la palabra "comprende" y sus variantes no pretenden excluir otras características técnicas, aditivos, componentes o pasos. Para los expertos en la materia, otros objetos, ventajas y características de la invención se desprenderán en parte de la descripción y en parte de la práctica de la invención. Los siguientes ejemplos y dibujos se proporcionan a modo de ilustración, y no se pretende que restrinjan la presente invención. Además, la presente invención cubre todas las posibles

combinaciones de realizaciones particulares y preferidas aquí indicadas.

# BREVE DESCRIPCIÓN DE LAS FIGURAS

- FIG. 1 muestra un esquema eléctrico simplificado del circuito propuesto en Dessouky, M.; Kaiser, A.; , "Input switch configuration suitable for rail-to-rail operation of switched op amp circuits," Electronics Letters , vol.35, no.1, pp.8-10, 7 Jan 1999.

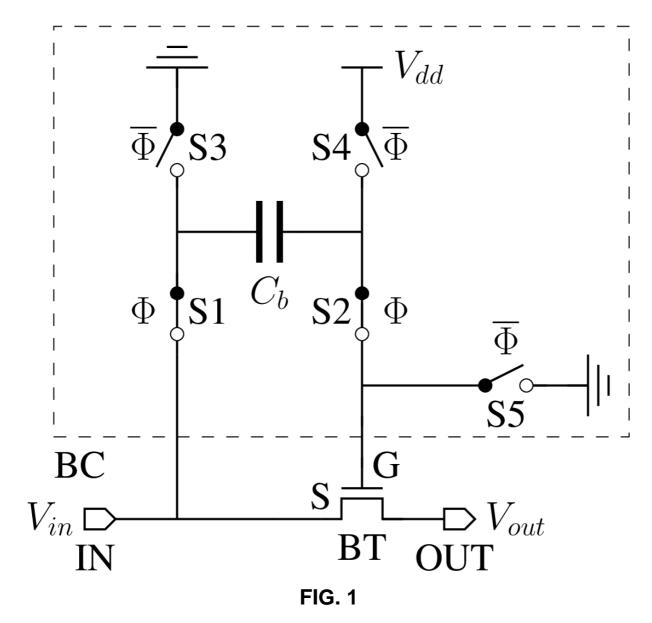

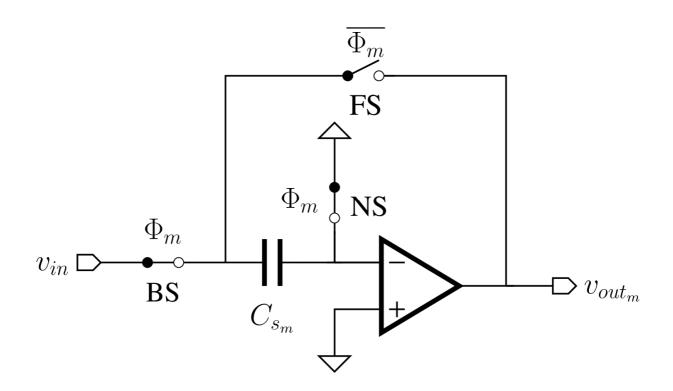

- FIG. 2 muestra un esquema eléctrico simplificado del circuito objeto de la invención, formado por un transistor BT (Bootstrapped Transistor) y un circuito BC (Bootstrapping Circuit).

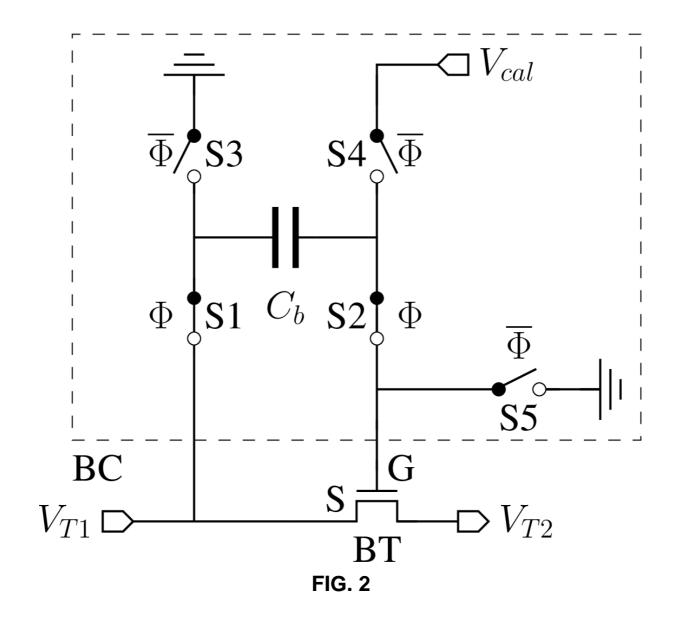

- FIG. 3 muestra una gráfica en la que se representa la evolución del valor de la resistencia entre los terminales T1 y T2 del transistor BT  $(r_{on})$ , en el eje vertical en ohmios  $(\Omega)$ , en función de  $V_{cal}$  representado en el eje horizontal en voltios (V).

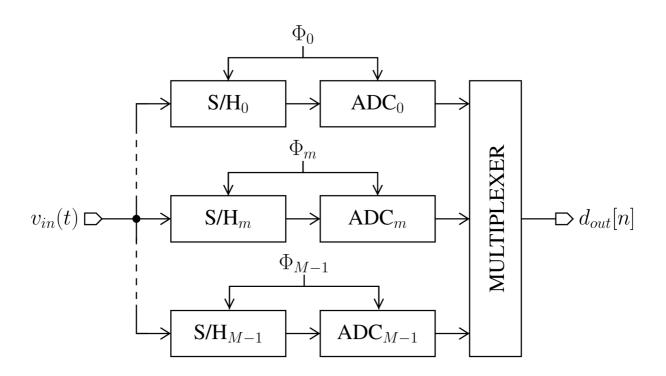

- FIG. 4 muestra un TI ADC (Time-Interleaved Analog-to-Digital Converter) formado por M vías o canales paralelos, donde cada vía está formada por un circuito de muestreo y amplificación (S/H $_m$ ) y un convertidor analógico-digital (ADC $_m$ ).

- FIG. 5 muestra un ejemplo de implementación de un circuito  $S/H_m$  como los mostrados en la figura 4.

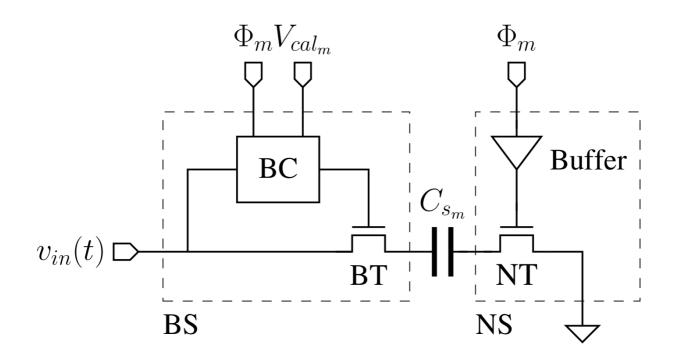

- FIG. 6 muestra un esquema de un circuito de muestreo RC en el que se ha incluido el interruptor BS (Bootstrapped Switch) objeto de la presente invención.

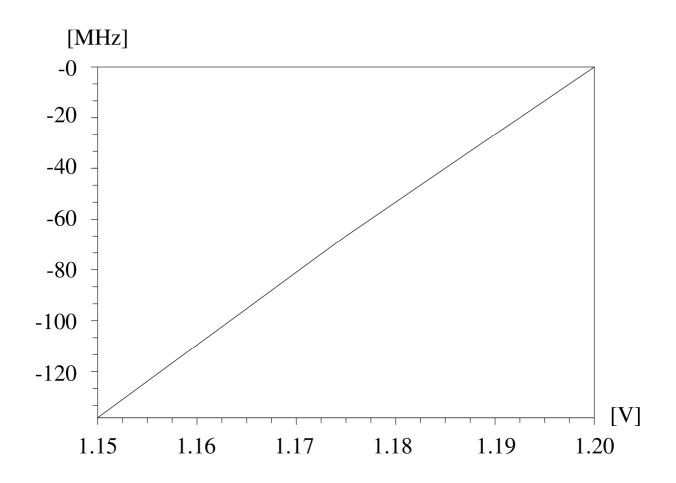

- FIG. 7 muestra la variación de  $f_{c3\text{-dBm}}$  nominal de un circuito de muestreo RC, representada en el eje vertical, en función del valor de  $V_{calm}$ , representado en el eje horizontal. (La variación de  $f_{c3\text{-dBm}}$ -nominal se ha calculado respecto al valor de  $f_{c3\text{-dBm}}$ -nominal tomado para  $V_{calm}$  = 1.2 V, que sirve como valor de referencia.)

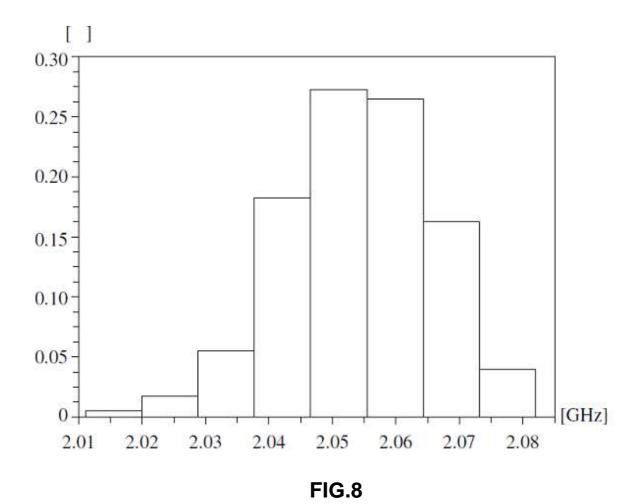

- FIG. 8 muestra el histograma de la distribución de los valores reales de  $f_{c3\text{-dBm}}$  que cabe esperar tras ser modificados por imperfecciones durante el proceso de fabricación, cuando  $V_{calm}$  se establece a 1.20 V.

30

25

15

# EXPOSICIÓN DETALLADA DE MODOS DE REALIZACIÓN Y EJEMPLO

El interruptor de la presente invención tiene una resistencia en estado cerrado que es variable mediante una señal de calibración externa estando la tensión de puerta elegida entre muchos valores posibles. Este interruptor, entre otros, soluciona el problema de disparidad en el ancho de banda de circuitos de muestreo RC. La necesidad de evitar ese problema viene dada porque esto puede limitar la linealidad con la que un TI ADC (convertidor analógico-digital basado en entrelazamiento temporal) es capaz de digitalizar señales analógicas.

10

5

El interruptor de la presente invención se aprecia en la figura 2 donde se presenta un esquema eléctrico simplificado del circuito, formado por un transistor BT y un circuito BC. Este esquema se basa en el interruptor descrito en la publicación de Dessouky (figura 1) sobre el que se han realizado las modificaciones necesarias para resolver el problema de linealidad con la que un TI ADC es capaz de digitalizar señales analógicas.

15

Más concretamente, el circuito BC comprende una pluralidad de interruptores (S1, S2, S3, S4, S5) conectados con una tensión de interrupción que abre ( $/\Phi$ ) y cierra ( $\Phi$ ) dichos interruptores; una entrada en tensión ( $V_{cal}$ ), donde dichos interruptores forman un puente en H con una capacidad Cb conectada en paralelo entre ambas ramas del puente; y donde un quinto interruptor S5 a masa está conectado en paralelo a la salida de un segundo interruptor S2 y a la puerta (G) del transistor BT, mientras que la primera rama del puente formada por el primer y tercer interruptor (S1,S3) está conectada en paralelo con la fuente (S) del transistor BT.

25

20

Gracias al esquema mostrado en la figura 2 es posible variar el valor de la resistencia entre los terminales T1 y T2 ( $r_{on}$ ) mediante la variación de  $V_{cal}$ . Así pues, y con respecto al esquema de la figura 1, se ha sustituido la tensión fija  $V_{dd}$  que se aplicaba en los circuitos del estado de la técnica por una tensión variable  $V_{cal}$  que es ahora la tensión de entrada del circuito. Aplicar la tensión variable  $V_{cal}$  permite variar indirectamente el valor de  $r_{on}$ .

30

35

Cuando se trabaja con valores de tensión en los interruptores ( $\Phi$ ) próximos al valor de  $V_{dd}$  (tensión fija de entrada), los interruptores internos S3, S4 y S5 se encuentran en estado abierto y los interruptores internos S1 y S2 se encuentran en estado cerrado. En esta situación la tensión entre los terminales del transistor BT ( $V_{GS}$ ) es igual a la tensión

acumulada entre las placas de la capacidad  $C_b$  (Vc<sub>b</sub>). El transistor BT es el interruptor que controla la conmutación de los terminales T1 y T2 y en general para valores de tensión  $\Phi$  próximos al valor de  $V_{dd}$ , BT se encuentra en estado cerrado, por lo que  $r_{on}$  (resistencia vista desde los terminales T1 y T2) tiene un valor bajo y depende de la tensión  $Vc_b$ .

5

10

Cuando se trabaja con valores de tensión  $\Phi$  próximos a la tensión de masa, los interruptores internos S3, S4 y S5 están en estado cerrado y los interruptores internos S1 y S2 están en estado abierto. En esta situación,  $Vc_b$  es igual a  $V_{cal}$ . El transistor BT está en estado abierto dado que  $V_{GS}$  es igual o inferior a cero voltios por la conexión a masa del terminal G del transistor a través del interruptor S5 (figura 2).

Al cambiar de nuevo el valor de tensión  $\Phi$  de nuevo a un valor próximo al valor de  $V_{dd}$ ,  $V_{GS}$  depende del valor de  $V_{cb}$  y este a su vez de  $V_{cal}$  en el estado anterior. Así pues, el punto de polarización y por tanto el valor de  $V_{cal}$  que es el objetivo de la presente invención.

20

15

En la figura 3 se muestra en una gráfica la evolución del valor de  $r_{on}$ , representado en el eje vertical en ohmios  $(\Omega)$ , en función de  $V_{cal}$ , representado en el eje horizontal en voltios (V). Esta gráfica se obtiene utilizando un transistor BT de anchura de 40  $\mu$ m y longitud de 0.06  $\mu$ m, en una tecnología CMOS estándar con  $V_{dd}$  igual a 1.20 V y una longitud de canal mínima de 65 nm. De ésta gráfica se desprende que  $r_{on}$  puede aumentar hasta un 28% en relación a su valor para  $V_{cal}$  igual a 1.2 V cuando  $V_{cal}$  cambia de 1.20 a 1.10 V.

25

En la figura 4 se aprecia un TI ADC formado por M vías o canales paralelos, nominalmente idénticos, en el que se representan explícitamente los bloques de los circuitos de muestreo y amplificación (S/H $_m$ ) que se colocan en la entrada de los circuitos de cuantificación de la señal analógica (ADC $_m$ ).

30

En la figura 5 se observa un ejemplo de implementación de un circuito de muestreo y amplificación  $S/H_m$  como los mostrados en la figura 4. Este circuito se ha realizado mediante capacidades conmutadas y un amplificador operacional. Dentro del bloque  $S/H_m$  se aprecia un circuito de muestreo RC formado por dos interruptores (BS y NS), y por una capacidad de muestreo  $Cs_m$ .

35

En la figura 6 se ha representado el esquema de un circuito de muestreo RC en el que se ha incluido el interruptor mostrado en la figura 2 y objetode la presente invención que está

formado por un transistor BT y un bloque BC como los que se muestran en la figura 2. Asimismo, este circuito de muestreo RC comprende una capacidad de muestreo Cs<sub>m</sub> y un interruptor NS que a su vez comprende un *Buffer* y un transistor NT.

5

10

20

25

30

Para comprobar los problemas que presenta el empleo de los interruptores conocidos del estado de la técnica se realizaron simulaciones de Monte Carlo (método no determinístico o estadístico numérico, usado para aproximar expresiones matemáticas complejas y costosas de evaluar con exactitud) para obtener la distribución que cabe esperar tras el proceso de fabricación de los valores de la frecuencia de corte a 3dB del circuito de muestreo RC ( $f_{\rm c3}$ - $_{\mathrm{dBm}}$ ), cuando  $V_{\mathit{cal}}$  se establece a 1.20 V para todas las M vías o canales paralelos  $(Vcal_m=1.20V para 0≤m≤M-1)$ . Las simulaciones se realizaron con una dimensión de  $W/L_{BT}=40/0.06$  para el transistor BT y  $W/L_{NT}=128/0.06$  para el transistor NT y un valor de  $Cs_m=2.5pF$  para la capacidad  $Cs_m$ . Estos valores se corresponden con los valores utilizados en la práctica en este tipo de circuitos RC con los que se puede obtener una relación señal a 15 ruido-distorsión nominal (SNDR<sub>nom</sub>) de hasta 85 dB para señales de entrada sinusoidales con una frecuencia ( $f_{in}$ ) de hasta 290 MHz.

Del análisis de la distribución (ver figura 8) se obtiene que el valor medio de  $f_{c3-dBm}$  es de 2.05 GHz., la desviación estándar relativa al valor medio ( $\sigma_r$ ) es del 0.6% y la diferencia entre los valores y mínimos de  $f_{c3-dBm}$  es de 70MHz. En base a los desarrollos descritos en el artículo de Sai-Weng Sin, con la variabilidad obtenida, la relación señal a ruido-distorsión promedia (SNDR) queda limitada a 64 dB para señales de entrada con  $f_{in}$ = 290 MHz, debido a las pérdidas de linealidad por causa de la disparidad del ancho de banda entre vías o canales de un TI ADC. Se trata de la distribución que cabe esperar tras el proceso de fabricación de los valores de la frecuencia de corte a 3dB del circuito de muestreo RC (fc3dBm), cuando  $V_{calm}$  se establece a 1.20 V. Ver adjunto.

Dichas pérdidas de linealidad se resuelven mediante el uso de M interruptores como el de la presente invención, de manera que sea posible ajustar los valores de  $V_{\it cal}$  hasta que los valores de  $f_{c3\text{-dBm}}$  sean lo suficientemente similares entre sí según el SNDR requerido en cada aplicación.

No obstante, el interruptor descrito por sí solo no resuelve el problema. La solución consta de dos partes:

- (a) Ser capaz de ajustar /modificar las características de los interruptores, tal y como se ha descrito para el interruptor objeto de la invención; y

- (b) Ser capaz de detectar el error para guiar al sistema de ajuste.

15

20

- Esta segunda parte esta fuera del alcance de la invención ya que existen técnicas en el estado de la técnica actual para la detección del error, que son compatibles y/o combinables con el objeto de la presente invención.

- Es por ello que el ajuste de  $V_{calm}$  en cada momento dependerá precisamente de estas técnicas de detección del error y su variación vendrá determinada por dicha etapa. El objeto de la invención y el problema técnico que resuelve es el ajuste de las características eléctricas del interruptor para las aplicaciones indicadas.

- En la figura 7 se muestra la variación de  $f_{c3\text{-dBm}}$  nominal (representado en el eje vertical en MHz) en función del valor de  $V_{calm}$  (representado en el eje horizontal en V). (La variación de  $f_{c3\text{-dBm}}$ -nominal se ha calculado respecto al valor de  $f_{c3\text{-dBm}}$ -nominal tomado para  $V_{calm} = 1.2$  V, que sirve como valor de referencia.) En la gráfica se aprecia que una variación de 30mV del valor de  $V_{calm}$  a partir de 1.20 V es suficiente para obtener una variación de hasta 80 MHz del valor de  $f_{c3\text{-dBm}}$ . En este caso, la variación de  $f_{c3\text{-dBm}}$  obtenida es suficiente para cubrir un rango de 70 MHz, como se había observado en las simulaciones de Monte Carlo, y por otra parte, la variación de 30mV del valor de  $V_{calm}$  a partir de 1.20 V es despreciable desde el punto de vista de la linealidad de cada circuito de muestreo RC estudiado por separado.

#### **REIVINDICACIONES**

5

10

15

20

25

30

- 1.- Interruptor con resistencia modificable que comprende al menos un transistor (BT) con una resistencia equivalente en estado cerrado entre terminales  $(r_{on})$ , conectado con un circuito (BC) que tiene una tensión de entrada variable (Vcal), y comprende una pluralidad de interruptores (S1, S2, S3, S4, S5) conectados con una tensión de interrupción ( $\Phi$ ) que abre y cierra dichos interruptores; y donde los citados interruptores están conectados en un puente en H, donde una primera rama está conformada por el tercer y primer interruptor (S3,S1) y una segunda rama formada por los interruptores cuarto y segundo (S4,S2); y que además comprende una capacidad ( $C_b$ ) conectada en paralelo entre ambas ramas del puente; y donde un quinto interruptor (S5) a masa está conectado en paralelo a la salida del segundo interruptor (S2) y a la puerta (G) del transistor (BT), mientras que la primera rama del puente formada por el primer y tercer interruptor (S1,S3) está conectada en paralelo con la fuente (S) del transistor (BT); caracterizado por que la resistencia entre terminales ( $r_{on}$ ) es proporcional a la tensión de entrada variable (Vcal) del circuito (BC).

- 2.- Interruptor de acuerdo con la reivindicación 1 donde con valores de tensión de interruptor ( $\Phi$ ) próximos a la tensión de masa, los interruptores internos tercero, cuarto y quinto (S3, S4 y S5) están en estado cerrado y los interruptores internos primero y segundo (S1 y S2) están en estado abierto; de tal forma que la tensión en la capacidad ( $Vc_b$ ) es igual a la tensión de calibración ( $V_{cal}$ ) y donde el transistor (BT) está en estado abierto dado que su tensión ( $V_{GS}$ ) es igual o inferior a cero voltios por la conexión a masa de la puerta (G) del transistor (BT) a través del quinto interruptor (S5); y donde al cambiar de nuevo el valor de tensión de los interruptores ( $\Phi$ ) de nuevo a un valor próximo al valor de tensión fija de entrada ( $V_{cd}$ ), la tensión del transistor ( $V_{GS}$ ) depende del valor de la tensión de la capacidad ( $Vc_b$ ) y este a su vez de la tensión de calibración ( $V_{cal}$ ) en el estado anterior.

- 3.- Uso del interruptor de acuerdo con las reivindicaciones 1 y 2 en un circuito de muestreo RC.

- 4.- Uso del interruptor de acuerdo con las reivindicaciones 1 y 2 en un convertidor analógico-digital basado en entrelazamiento temporal.

(ESTADO DE LA TÉCNICA)

FIG. 4

FIG. 5

FIG. 6

FIG. 7

16

(21) N.º solicitud: 201330067

22 Fecha de presentación de la solicitud: 22.01.2013

32 Fecha de prioridad:

# INFORME SOBRE EL ESTADO DE LA TECNICA

| ⑤ Int. Cl. : | <b>H03K17/687</b> (2006.01) |

|--------------|-----------------------------|

|              |                             |

#### **DOCUMENTOS RELEVANTES**

| Categoría         | <b>66</b>                                                                                                                                                      | Documentos citados                                                                                                                                                                                  | Reivindicacione<br>afectadas |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|

| Х                 | EP 1608069 A2 (COMMISSARIAT ENERGIE ATOMIQUE) 21.12.2005, figura 2; resumen; descripción.                                                                      |                                                                                                                                                                                                     | 1-4                          |  |

| А                 |                                                                                                                                                                | Spectra and Distortion Analysis of Time-Interleaved Sampling Systems II: Express Briefs, IEEE Transactions on, vol. 55, 10.1109/TCSII.2008.921600.                                                  | 1-4                          |  |

| Υ                 | DESSOUKY, M.; KAISER, A., "I switched op amp circuits," Electron doi: 10.1049/el:19990028.                                                                     | SER, A., "Input switch configuration suitable for rail-to-rail operation of s," Electronics Letters, vol. 35, no. 1, pp. 8,10, 7 Enero 1999; 28.                                                    |                              |  |

| Y                 | US 2008136495 A1 (CORNELISSE descripción; figuras.                                                                                                             | 1-4                                                                                                                                                                                                 |                              |  |

|                   |                                                                                                                                                                |                                                                                                                                                                                                     |                              |  |

|                   |                                                                                                                                                                |                                                                                                                                                                                                     |                              |  |

|                   |                                                                                                                                                                |                                                                                                                                                                                                     |                              |  |

| X: d<br>Y: d<br>r | egoría de los documentos citados<br>le particular relevancia<br>le particular relevancia combinado con ot<br>nisma categoría<br>efleja el estado de la técnica | O: referido a divulgación no escrita ro/s de la P: publicado entre la fecha de prioridad y la de pr de la solicitud E: documento anterior, pero publicado después d de presentación de la solicitud |                              |  |

|                   | presente informe ha sido realizado<br>para todas las reivindicaciones                                                                                          | para las reivindicaciones nº:                                                                                                                                                                       |                              |  |

| Fecha             | de realización del informe<br>16.06.2014                                                                                                                       | <b>Examinador</b><br>M. P. López Sabater                                                                                                                                                            | Página<br>1/4                |  |

# INFORME DEL ESTADO DE LA TÉCNICA Nº de solicitud: 201330067 Documentación mínima buscada (sistema de clasificación seguido de los símbolos de clasificación) H03K Bases de datos electrónicas consultadas durante la búsqueda (nombre de la base de datos y, si es posible, términos de búsqueda utilizados) INVENES, EPODOC, IEEE, Internet, Inspec

**OPINIÓN ESCRITA**

Nº de solicitud: 201330067

Fecha de Realización de la Opinión Escrita: 16.06.2014

Declaración

Novedad (Art. 6.1 LP 11/1986)

Reivindicaciones 1-4

SI

Reivindicaciones NO

Actividad inventiva (Art. 8.1 LP11/1986) Reivindicaciones SI

Reivindicaciones 1-4 NO

Se considera que la solicitud cumple con el requisito de aplicación industrial. Este requisito fue evaluado durante la fase de examen formal y técnico de la solicitud (Artículo 31.2 Ley 11/1986).

#### Base de la Opinión.-

La presente opinión se ha realizado sobre la base de la solicitud de patente tal y como se publica.

Nº de solicitud: 201330067

#### 1. Documentos considerados.-

A continuación se relacionan los documentos pertenecientes al estado de la técnica tomados en consideración para la realización de esta opinión.

| Documento | Número Publicación o Identificación                                                                                                                                                                            | Fecha Publicación |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| D01       | EP 1608069 A2 (COMMISSARIAT ENERGIE ATOMIQUE)                                                                                                                                                                  | 21.12.2005        |

| D02       | DESSOUKY, M.; KAISER, A., "Input switch configuration suitable for rail-to-rail operation of switched op amp circuits," Electronics Letters, vol. 35, no. 1, pp. 8,10, 7 Enero 1999; doi: 10.1049/el:19990028. |                   |

| D03       | US 2008136495 A1 (CORNELISSENS KOEN et al.)                                                                                                                                                                    | 12.06.2008        |

# 2. Declaración motivada según los artículos 29.6 y 29.7 del Reglamento de ejecución de la Ley 11/1986, de 20 de marzo, de Patentes sobre la novedad y la actividad inventiva; citas y explicaciones en apoyo de esta declaración

#### Reivindicación 1:

En el documento del estado de la técnica D01 se divulga, en su figura 2, un interruptor con resistencia modificable que comprende al menos un transistor con una resistencia equivalente en estado cerrado entre terminales, que comprende una pluralidad de interruptores (22,24,32,34,28) conectados con una tensión de interrupción que abre y cierra dichos interruptores y donde los citados interruptores están conectados en un puente en H. Una primera rama está conformada por el tercer y primer interruptor (26,34) y una segunda rama está formada por los interruptores cuarto y segundo (24,32). El circuito comprende además una capacidad (20) conectada en paralelo entre ambas ramas del puente y un quinto interruptor (28) a masa que está conectado en paralelo a la salida del segundo interruptor (32) y a la puerta (22) del transistor. La primera rama del puente, la formada por el primer y tercer interruptor (26,34), está conectada en paralelo con la fuente del transistor. La resistencia entre terminales resulta, como consecuencia de esta configuración, proporcional a la tensión de entrada del circuito, Vdd.

La única diferencia entre el circuito de D01 y el de esta reivindicación consiste en que la tensión aplicada a la entrada del circuito que se desea proteger se hace variable.

A consecuencia de esta diferencia, el circuito de D01 sufre de una cierta falta de linealidad que resulta un inconveniente, especialmente, y según se dice en el propio documento, para aplicaciones relativas a telecomunicaciones.

Para resolver el problema técnico que se deriva de esta diferencia, los solicitantes de D01 proponen, según el resumen del documento, mejorar el circuito de la figura 2 aplicando una tensión a la entrada variable en vez de la tensión constante Vdd.

En la descripción se propone la opción de que los distintos valores de tensión sean aplicados a través de dos condensadores diferentes en vez de uno solo. Sin embargo, no se descarta incorporar la modificación de la fuente de tensión en el circuito original para conseguir el efecto técnico deseado. (Descripción de D01, párrafo [0040])

A la vista de todo lo anterior, esta primera reivindicación carece de actividad inventiva según el artículo 8 de la Ley de Patentes 11/86.

Si en vez de considerar el documento D01 se considerasen los documentos D02 y D03 se llegaría a la misma conclusión, puesto que en D02 de nuevo se presenta un circuito que es idéntico al que se desea proteger salvo por la fuente de tensión fija. A consecuencia de esta diferencia, como se ha indicado anteriormente, este circuito adolece de una falta de linealidad que afecta a varias de sus aplicaciones posibles.

En el documento D03 se propone, como medio para solucionar este problema técnico, la variación de la tensión de entrada. Un experto en la materia que deseara solucionar el problema del circuito de D02 no tendría que ejercer actividad inventiva alguna para incorporar en éste la solución aportada por D03, llegando así al mismo circuito que se desea proteger en esta primera reivindicación.

#### Reivindicación 2:

Esta reivindicación, dependiente de la anterior, describe cómo actúan los elementos que componen el circuito que se desea proteger cuando se les aplican unas tensiones u otras.

El comportamiento de los elementos del circuito es la consecuencia de la topología del mismo y de las señales que recibe y, por lo tanto, no tiene actividad inventiva alguna.

#### Reivindicaciones 3 y 4:

Al carecer de actividad inventiva, la incorporación del interruptor reivindicado en un aparato, no confiere a este último actividad inventiva alguna.