(1) Número de publicación: 2 193 851

21) Número de solicitud: 200101834

(51) Int. Cl.<sup>7</sup>: H03L 7/085 H03L 7/181

# © SOLICITUD DE PATENTE

Α1

- 22 Fecha de presentación: 03.08.2001

- 43 Fecha de publicación de la solicitud: 01.11.2003

- Fecha de publicación del folleto de la solicitud: 01.11.2003

- 71 Solicitante/s: Universidad de Málaga Plaza de El Ejido, s/n 29071 Málaga, ES

- Inventor/es: Romero Sánchez, Jorge; Fernández Ramos, Raquel N.; Ríos Gómez, Francisco J. y Martín Canales, José Francisco

- 74 Agente: No consta.

- 54 Título: Circuito integrado sintetizador de frecuencias.

(57) Resumen:

Circuito integrado sintetizador de frecuencias. Circuito integrado sintetizador de frecuencias, basado en técnica Phase-Locked Loop (PLL), cuyo objetivo es el control de frecuencias en aquellos sistemas que requieran una conmutación rápida de canal

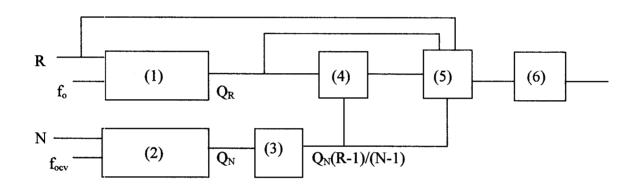

Este circuito consta de un registro divisor de frecuencias con módulo programable R, para la frecuencia del oscilador de referencia (1); un registro divisor de frecuencias con módulo programable N, para la frecuencia del oscilador controlado por voltaje (2), un módulo de escalado (3), un restador de fase (4), un módulo corrector de fase (5), y un conversor digital/analógico (6).

10

15

20

30

45

55

65

# 1 DESCRIPCION

Circuito integrado sintetizador de frecuencias. Sector de la técnica

La presente invención tiene su aplicación en aquellos sistemas que requieran un control de frecuencias y, en especial, en los que sea imprescindible una conmutación de canales a velocidad elevada. Estos sistemas se encuentran en equipos de radiocomunicación de espectro ensanchado, telefonía celular, relojes de precisión, equipos de medicina, satélites de comunicaciones, etc.

#### Estado de la técnica

Un PLL es un circuito en lazo cerrado utilizado para controlar con precisión los parámetros frecuencia y fase de un oscilador cuya frecuencia se puede variar mediante un voltaje. Este sistema está inspirado en los clásicos servomecanismos de control de posición y de velocidad de un motor mecánico (Ogata K. *Modern Control Engineering* 2ª Ed. Prentice-Hall International Editions 1990. Capítulos 1,2,4). El funcionamiento básico es el siguiente:

A partir de una señal periódica con parámetros a controlar, frecuencia y fase, que procede de un oscilador de precisión llamado oscilador de referencia, se genera otra señal periódica de frecuencia  $f_o$  dividida por un factor entero R denominada frecuencia de referencia  $f_{ref}$ . La división se realiza mediante un divisor de frecuencias programable de módulo R. La relación entre  $f_o$  y  $f_{ref}$ es, precisamente,  $f_{ref} = f_o/R$ . Esta frecuencia de referencia es comparada con otra, procedente del oscilador controlado por voltaje, a la que llamaremos  $f_{ocv}$  y que previamente se ha dividido por un factor entero N mediante otro divisor de frecuencias. Se tiene, pues, como elementos comparados  $f_{ref}$  y  $f_{ocv}/N$ . La operación de comparación, en primera aproximación, es la diferencia entre las fases asociadas a cada señal, y el dispositivo que realiza la comparación es el detector de fase. Bajo condiciones de estabilidad asociadas a sistemas lineales (Oppertheim A. V., Willsky A. S., Young I. T. Signals and Systems Prentice-Hall International Editions 1983. Capítulo 9) se tiene que, en situación equilibrio, las señales comparadas poseen igual frecuencia pero diferente fase, la cual, es continuamente comparada en el detector de fase. Esta diferencia de fase es filtrada mediante un filtro paso-bajas y empleada para corregir cualquier perturbación que se produzca sobre la señal generada por el oscilador controlado por tensión. La relación entre la frecuencia  $\mathbf{f}_{ocv}$ , la frecuencia  $\mathbf{f}_{ref}$  y la frecuencia  $\mathbf{f}_o$  es precisamente:  $\mathbf{f}_{ocv} = \mathbf{N}\mathbf{f}_{ref} = \mathbf{N}\mathbf{f}_o/\mathbf{R}$  (Smith J. Modern Communication Circuits McGraw-Hill International Editions 1986. Capítulos 8,10).

Sin embargo, este tipo de PLL no es la solución ideal para síntesis de frecuencias en la que se precise cambiar de canal de forma rápida (cambiar de canal implica cambiar el módulo de división N), ya que el filtro paso-bajas necesita atenuar de forma pronunciada las componentes de señal cuya frecuencia es proporcional a  $f_{ref}$  y que aparecen de forma inevitable a la salida del detector de fase: éstas son las señales espúreas. Por ello, la frecuencia de corte del filtro paso-bajas ha de reducirse, si se quiere atenuar tales com-

ponentes y, como consecuencia, la velocidad de conmutación de canal disminuye. Por otro lado el ruido de fase generado en este tipo de PLL es elevado.

Para solucionar el problema de la velocidad de conmutación se han de abordar técnicas basadas en PLL más complejas y caras, como la síntesis digital directa o los PLL con múltiple lazo, o combinaciones de ambos. Pero este tipo de variaciones también deterioran inexorablemente el ruido de fase y, por tanto, la calidad de la señal generada (Smith J. Modern Communication Circuits McGraw-Hill International Editions 1986. Capítulo 10).

Marc Zuta en su artículo A New PLL With Fast Settling Time and Low Phase Noise (Microwave Journal Euro-Global Edition, Junio 1998, Vol. 41, No 6. Páginas 94-108), propone una solución basada en el PLL básico descrito, que aprovecha más información de los divisores de frecuencia de módulo programables que generan las frecuencias  $f_{ref}$  y  $f_{ocv}/N$ , además propone un método de detección de fase lineal basado en una resta directa, todo ello de forma digital y empleando un procesador de señales digitales. Con esta solución, se puede diseñar el filtro paso-bajas con una frecuencia de corte mucho más elevada y unas características de atenuación menos restrictivas, permitiendo una solución de diseño del mismo de bajo coste, y aumentando la velocidad de conmutación de canal del sintetizador de forma drástica. El sistema propuesto por Zuta, sin embargo, tiene la restricción de que, en estado de equilibrio, la diferencia de fases de las señales comparadas ha de ser nula, ya que en caso contrario, de nuevo generarían señales espúreas con frecuencia proporcional a  $f_{ref}$  a la salida del mismo, todo ello debido a que se compara exclusivamente el valor principal de la fase, el cual está comprendido entre 0 y  $2\pi$  radianes. Como consecuencia de esta restricción el filtro paso-bajas se ha de diseñar de forma que genere un estado de equilibrio con diferencia de fase nula, o lo que es lo mismo, un PLL de Tipo II (Smith J. Modern Communication Circuits McGraw-Hill International Editions 1986. Capítulo 9).

En esta invención, y basándose en el modelo desarrollado por Zuta, se propone un dispositivo de corrección de fase que permite operar con diferencias de fase no nulas en general, sin generar señales espúreas, permitiendo el uso de filtros paso-bajas extremadamente sencillos (PLL de Tipo I), lo cual implica un ahorro económico y de tiempo de diseño sobre otras topologías más complejas. Además se integra el sistema de síntesis de frecuencia completo en un circuito integrado monolítico.

Hacer notar que los inventores no tienen conocimiento, hasta el momento actual, de un circuito integrado de síntesis de frecuencia que haga uso de este método de corrección de fase.

Explicación de la invención

El circuito integrado propuesto plantea una solución como sintetizador de frecuencias con una simplicidad elevada y de altas prestaciones que incluyen, bajo ruido de fase, alta velocidad de conmutación de canal, en sistemas PLL con lazo simple. Todo ello se integra en un único circuito mo-

5

10

15

20

25

30

35

45

50

55

60

65

En concreto, este circuito integrado está comprendido por una serie de módulos funcionales que lo configuran para la realización de la síntesis de frecuencia en un sistema PLL. A saber:

- Registro divisor de frecuencias con módulo programable R para la frecuencia del oscilador de referencia.

- Registro divisor de frecuencias con módulo programable N para la frecuencia del oscilador controlado por voltaje.

- Módulo de escalado.

- Módulo restador de fase.

- Módulo corrector de fase.

- Conversor digital/analógico.

En los registros divisores de frecuencia con módulos programables correspondientes al oscilador de referencia y al oscilador controlado por voltaje, respectivamente, se divide el parámetro frecuencia de cada una de las señales aportadas por los respectivos osciladores por los factores R y N para generar  $f_{ref} = f_{ocv}/N$ .

Sobre la información de fase obtenida a la salida del divisor de frecuencia correspondiente al oscilador controlado por voltaje se realiza, en primer lugar, un proceso de escalado en el módulo de escalado del sintetizador. El factor de escala es la división R/N. Esta información de fase, una vez escalada, se compara con la información de fase obtenida del divisor de frecuencias correspondiente al oscilador de referencia.

Dicha comparación ocurre en el módulo restador de fase obteniéndose, como resultado, la diferencia de ambas fases, la cual será modificada por el módulo corrector de fase para obtener de esta manera, la diferencia de fase continua y no su valor principal (que tenía el problema de la generación de señales espúreas o indeseadas).

Por último, la información correcta de fase es aplicada al conversor digital/analógico y presentada a la salida del circuito integrado.

#### Descripción de los dibujos

Para facilitar la comprensión de la descripción, se ha incluido en la presente memoria una hoja con una única figura en la que se ilustra el diagrama de bloques funcionales de la invención.

#### Realización preferente de la invención

Tal y como se muestra en la figura única el circuito integrado para síntesis de frecuencia, objeto de esta invención, está configurado con los módulos funcionales necesarios para realizar el proceso de control de frecuencias para el cual está pensado. Los módulos que lo componen son los siguientes:

• Registro divisor de frecuencias con módulo programable R para la frecuencia del oscilador de referencia (1).

- Registro divisor de frecuencias con módulo programable N para la frecuencia del oscilador controlado por voltaje (2).

- Módulo de escalado (3).

- Módulo restador de fase (4).

- Módulo corrector de fase (5).

- Conversor digital/analógico (6).

En los registros divisores de frecuencia con módulos programables (1) y (2) correspondientes al oscilador de referencia y al oscilador controlado por voltaje, respectivamente, se divide el parámetro frecuencia de cada una de las señales aportadas por los respectivos osciladores por unos factores para generar  $f_{ref} = f_o/R$  y  $f_{osc}/N$ , o de forma equivalente y en términos de fases, se obtienen  $\theta_{ref}$ , como la fase correspondiente a  $f_{ref}$ , y  $\theta_{ocv}$  como la fase correspondiente a  $f_{ocv}$ . Si contamos con toda la información de los registros divisores de frecuencia (1) y (2), se puede considerar que sus contenidos, llamémoslos  $Q_R$  para (1) y  $Q_N$  para (2), son una versión digital de las fases originales, y relacionadas de la siguiente forma:

$$\theta_{ref} = 2\pi Q_R/(R-1), y \theta_{ocv} = 2\pi Q_N/(N-1).$$

Con  $0 \le Q_R \le R$  -1  $y 0 \le Q_N \le R$  -1

Las relaciones de división por el módulo del correspondiente divisor de frecuencias (1) y (2) se siguen manteniendo para las fases, es decir, a la salida de sendos divisores obtenemos  $\theta_{ref} = \theta_o/R$  y  $\theta_{ocv}/N$ , donde  $\theta_o$  es la fase correspondiente a f<sub>o</sub>.

Sobre la información de fase obtenida a la salida del divisor de frecuencia correspondiente al oscilador controlado por voltaje se realiza, en primer lugar, un proceso de escalado sobre su contenido  $Q_N$  en el módulo de escalado (3) del sintetizador. El factor de escala es la división (R-1)/(N-1), se tiene, pues, a su salida  $Q_N(R-1)/(N-1)$ . Esta información de fase, una vez escalada, se compara con la información de fase obtenida del divisor de frecuencias correspondiente al oscilador de referencia, es decir,  $Q_R$ .

Dicha comparación ocurre en el módulo restador de fase (4) obteniéndose, como resultado, la diferencia de ambas fases  $\theta_{ref}$  -  $\theta_{ocv}$ , que en su forma digital sería  $Q_R$   $Q_N(R-1)/(N-1)$ . Esta información será modificada por el módulo corrector de fase (5) para obtener así, la diferencia de fase continua y no su valor principal (que tenía el problema de la generación de señales espúreas ó indeseadas). La fase, a la salida del sistema corrector de fase sería  $\theta_{ref}$  -  $\theta_{ocv}+\Delta\theta$ . Donde;  $\Delta\theta$  es el factor corrector de fase, el cual, en su forma digital  $\Delta Q$ , viene dado por la siguiente expresión:

$$\Delta {\bf Q} = 0 \text{ si } {\bf Q}_R \geq {\bf Q}_N({\bf R}\text{-}1)/({\bf N}\text{-}1)$$

$$\Delta {\bf Q} = {\bf R} \text{ si } {\bf Q}_R < {\bf Q}_N({\bf R}\text{-}1)/({\bf N}\text{-}1)$$

Por último, la información corregida de fase es aplicada al conversor digital/analógico (6) y presentada a la salida del circuito integrado.

## REIVINDICACIONES

1. Circuito integrado sintetizador de frecuencias, caracterizado porque consta de un registro divisor de frecuencias con módulo programable para la frecuencia del oscilador de referencia, un registro divisor de frecuencias con módulo programable para la frecuencia del oscilador controlado por voltaje, un módulo de escalado, un restador de fase, un módulo corrector de fase, y un con-

versor digital/analógico.

2. Circuito integrado sintetizador de frecuencias, según la primera reivindicación, **caracterizado** porque mediante el módulo corrector de fase se obtiene una diferencia de fase continua y no su valor principal. El algoritmo de corrección es:

$$\Delta Q = 0 \text{ si } Q_R \ge Q_N(R-1)/(N-1)$$

$$\Delta Q = R \text{ si } Q_R < Q_N(R-1)/(N-1)$$

Figura Única

① ES 2 193 851

$\begin{tabular}{ll} \hline (21) & N.^\circ & solicitud: & 200101834 \\ \hline \end{tabular}$

22) Fecha de presentación de la solicitud: 03.08.2001

(32) Fecha de prioridad:

## INFORME SOBRE EL ESTADO DE LA TECNICA

| (51) Int. Cl. <sup>7</sup> : | H03L 7/085, 7/181 |  |  |

|------------------------------|-------------------|--|--|

|                              |                   |  |  |

|                              |                   |  |  |

## **DOCUMENTOS RELEVANTES**

| Categoría           |                                                                                                                                                                                                                                                                                                                                                                   | Documentos citados                                        | Reivindicaciones<br>afectadas |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------|

| X<br>A              | WO 9844632 A1 (ZUTA, MAR                                                                                                                                                                                                                                                                                                                                          | VO 9844632 A1 (ZUTA, MARK) 08.10.1998, todo el documento. |                               |

| Α                   | US 5999060 A (ZUTA) 07.12.1                                                                                                                                                                                                                                                                                                                                       | 1999, todo el documento.                                  | 1,2                           |

| Α                   | US 6188288 B1 (RAGAN et al.                                                                                                                                                                                                                                                                                                                                       | ) 13.02.2001, todo el documento.                          | 1,2                           |

| Α                   | US 6198353 B1 (JANESCH et                                                                                                                                                                                                                                                                                                                                         | 1,2                                                       |                               |

|                     |                                                                                                                                                                                                                                                                                                                                                                   |                                                           |                               |

|                     |                                                                                                                                                                                                                                                                                                                                                                   |                                                           |                               |

| X: de<br>Y: de<br>m | Categoría de los documentos citados  X: de particular relevancia  Y: de particular relevancia combinado con otro/s de la misma categoría  A: refleja el estado de la técnica  C: referido a divulgación no escrita  P: publicado entre la fecha de prioridad y la de de la solicitud  E: documento anterior, pero publicado despu de presentación de la solicitud |                                                           |                               |

| El pr               | resente informe ha sido realiza<br>] para todas las reivindicaciones                                                                                                                                                                                                                                                                                              | para las reivindicaciones n°:                             |                               |

| Fecha d             | le realización del informe<br>29.09.2003                                                                                                                                                                                                                                                                                                                          | <b>Examinador</b><br>J. Botella Maldonado                 | Página<br>1/1                 |