OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 180 386**

(21) Número de solicitud: 200001982

(51) Int. Cl.<sup>7</sup>: **H05B 41/288**

(12)

PATENTE DE INVENCIÓN

B1

(22) Fecha de presentación: **31.07.2000**

(43) Fecha de publicación de la solicitud: **01.02.2003**

Fecha de la concesión: **08.03.2004**

(45) Fecha de anuncio de la concesión: **01.04.2004**

(45) Fecha de publicación del folleto de la patente:

**01.04.2004**

(73) Titular/es: **Universidad de Oviedo,

Plaza del Riego, 4 (Edificio Histórico)

33003 Oviedo, Asturias, ES**

(72) Inventor/es: **Ribas Bueno, Javier;

Alonso Álvarez, José Marcos y

Calleja Rodríguez, Antonio Javier**

(74) Agente: **No consta**

(54) Título: **Dos circuitos electrónicos para alimentación de lámparas de descarga con corrección activa del factor de potencia basados en topologías de una sola etapa.**

(57) Resumen:

Dos circuitos electrónicos para alimentación de lámparas de descarga con corrección activa del factor de potencia basados en topologías de una sola etapa, que pueden ser empleados para el diseño de balastos electrónicos de bajo coste.

Los dos circuitos provienen de la integración en una sola etapa de un convertidor reductor y un inversor resonante en puente completo y se caracterizan por tener una baja distorsión armónica de la corriente de entrada y por alimentar la lámpara con una señal alterna de alta frecuencia y bajo factor de cresta, lo cual permite un mejor aprovechamiento de la vida útil de la misma. Los circuitos objeto de la invención presentan un coste inferior a los utilizados actualmente debido a que el número total de componentes es menor y a que la circuitería de control es más simple. De aplicación en el sector de iluminación.

ES 2 180 386 B1

Aviso: Se puede realizar consulta prevista por el art. 37.3.8 LP.

## DESCRIPCION

Dos circuitos electrónicos para alimentación de lámparas de descarga con corrección activa del factor de potencia basados en topologías de una sola etapa.

### Campo de la invención

El objeto de la presente invención son dos circuitos electrónicos para la alimentación de lámparas de descarga de potencias comprendidas entre 85 y 400 vatios aproximadamente. Más en concreto, la invención está relacionada con los balastos electrónicos que generan una señal de alta frecuencia a partir de la señal de red y que presentan un alto factor de potencia y baja distorsión armónica. También es un objetivo importante la disminución del coste de estos equipos.

### Descripción del estado de la técnica

La función básica de los balastos para lámparas de descarga es la de proporcionar la sobreten-sión necesaria para el cebado y suministrar una corriente con bajo factor de cresta durante el funcionamiento normal. De esta forma se consigue aprovechar la totalidad de la vida útil de la lámpara. Los balastos deben a su vez cumplir la normativa relativa a la emisión de armónicos de baja frecuencia que limita el factor de potencia mínimo y la distorsión armónica admisible de la corriente de entrada. Otro factor a tener en cuenta es el rendimiento energético que presenta el balasto, puesto que, si el rendimiento es demasiado bajo, se pierde la ventaja que supone la elevada eficiencia lumínosa de las lámparas de descarga, además de producir una pérdida de energía en forma de calor que no resulta admisible para la mayoría de las aplicaciones.

Los balastos más ampliamente utilizados actualmente son de tipo electromagnético. Estos balastos son de volumen y peso elevados debido principalmente a que el elemento reactivo se encuentra devanado sobre un voluminoso núcleo de chapa metálica. Los balastos electrónicos presentan un volumen y un peso sensiblemente menor al de los balastos electromagnéticos. No obstante, sus principales ventajas son un rendimiento energético superior y un mejor aprovechamiento de las características de cada lámpara, lo cual permite incrementar su vida útil. Además, los balastos electrónicos pueden ser utilizados para ajustar la potencia entregada a la lámpara para adaptar el nivel de iluminación a las condiciones de uso con el consiguiente ahorro de energía. Estas ventajas están suponiendo un gran incremento del número de aplicaciones en las que se emplean actualmente balastos electrónicos en lugar de los balastos electromagnéticos convencionales.

Uno de los aspectos más importantes a tener en cuenta en el diseño de balastos electrónicos es el coste final del producto. Este debe ser lo más bajo posible puesto que este tipo de soluciones deben competir en el mercado con los balastos electromagnéticos tradicionales. Los balastos electromagnéticos presentan un rendimiento inferior y un menor aprovechamiento de la vida útil de la lámpara, pero presentan como principal ventaja un precio reducido.

Para obtener un balasto electrónico que combine las propiedades de elevado factor de potencia

en la entrada y bajo factor de cresta en la lámpara es habitual emplear dos convertidores en cascada. El primer convertidor incorpora un interruptor principal y los elementos reactivos necesarios para el almacenamiento de energía. Este primer convertidor se encarga de proporcionar un nivel de tensión continua estable, asegurando un elevado factor de potencia en la entrada. El segundo convertidor es de tipo inversor resonante y permite tanto provocar el encendido de la lámpara, como su alimentación en régimen permanente (J. Span-gler et al., "Electronic fluorescent ballast using power factor correction techniques for loads greater than 300 Watts", Applied Power Electronics Conference and Exposition, 1991). Sin embargo, estas soluciones presentan un elevado coste debido al gran número de componentes que incor-poran.

Una de las soluciones que comienzan a emplearse para reducir el precio de los balastos electrónicos proviene del empleo de convertidores de una sola etapa. En éstos se busca simplificar la circuitería de control y de potencia mediante convertidores que incorporan en una sola etapa un elevado factor de potencia y permiten alimentar la lámpara con bajo factor de cresta (H. Güldner, K. Lehnert et al., "Principles of electronic ballasts for fluorescent lamps", Power Electronics Specia-lists Conference, 1.999). El principal inconve-niente de este tipo de circuitos proviene de que al menos uno de los interruptores del circuito pre-senta esfuerzos elevados. Esto supone que, para el rango de potencias al que se encuentran ori-en-tados los circuitos de la presente invención, sea preciso el empleo de semiconductores de precio elevado.

### Breve descripción de las figuras

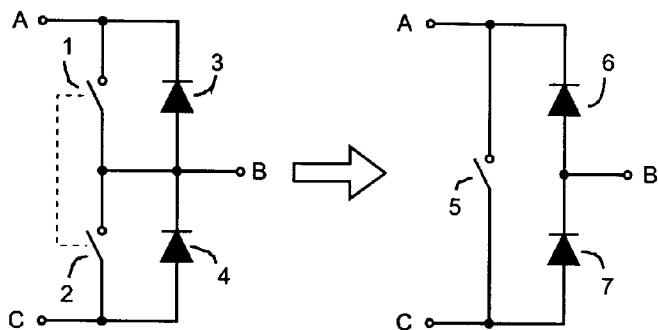

Las figuras 1.a y 1.b muestran las equivalencias empleadas en el proceso de integración utili-zado para la obtención de los circuitos objeto de la presente invención.

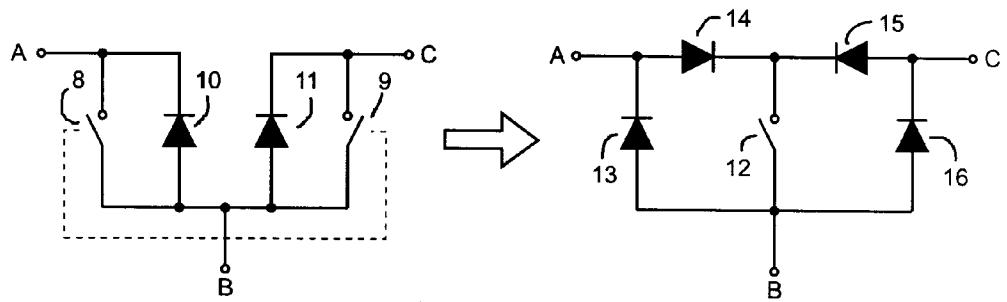

Las figuras 2.a a 2.c muestran las formas de onda básicas de un convertidor reductor funcio-nando en modo de conducción discontinuo em-pleado como etapa para corrección del factor de potencia. La figura 2.a muestra las tensiones de entrada y salida del convertidor. La figura 2.b re-presenta la forma de onda de la corriente por la inductancia y la figura 2.c muestra la corriente de entrada del convertidor tras aplicar un pequeño filtro.

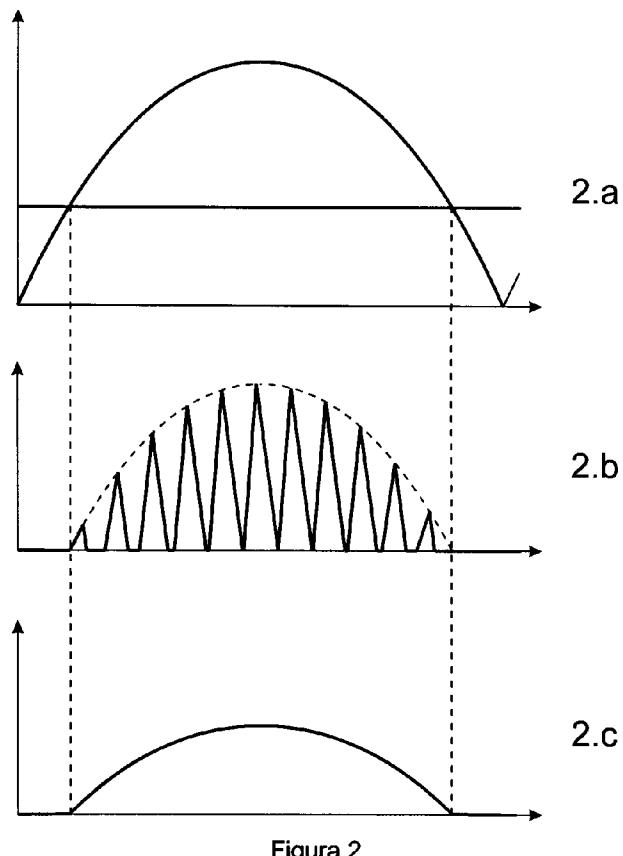

Las figuras 3.a a 3.d representan las formas de onda básicas correspondientes a un inversor resonante de puente completo. Las figuras 3.a y 3.b muestran la tensión y la corriente de entrada al circuito resonante respectivamente y las figuras 3.c y 3.d los pulsos de control de los interruptores del puente.

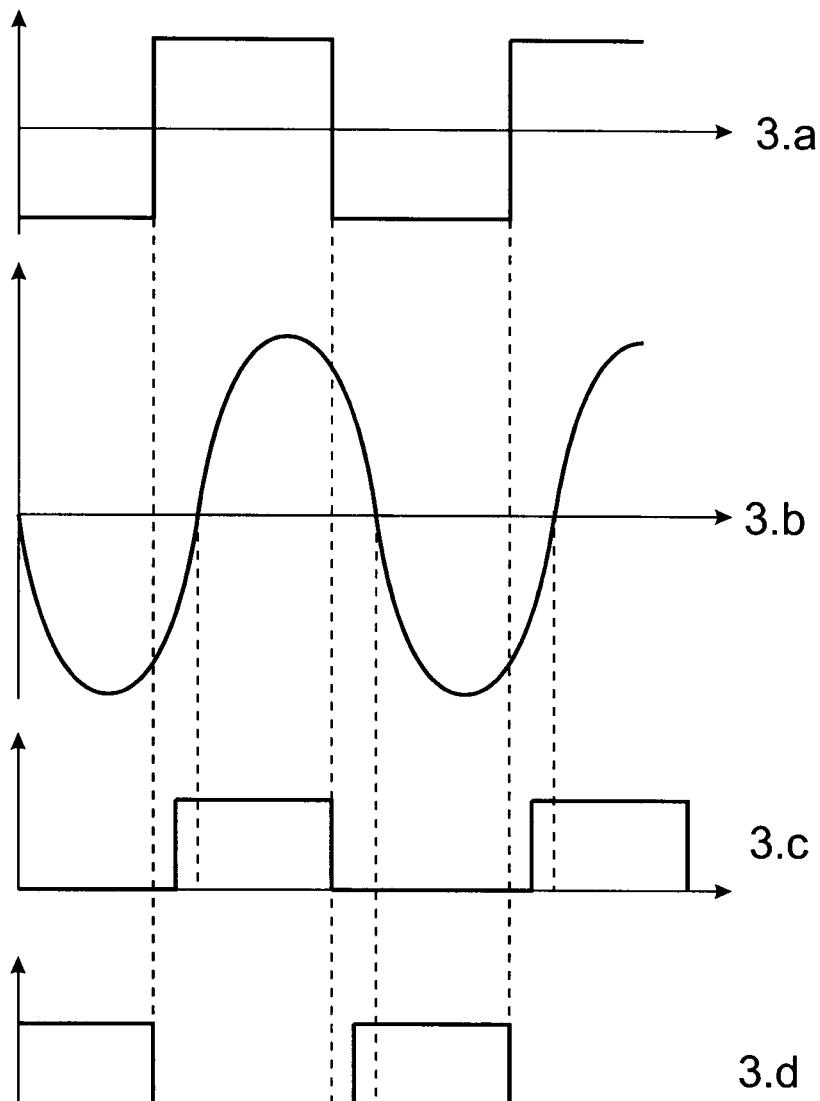

Las figuras 4.a, 4.b y 4.c muestran los pasos seguidos para la obtención de la primera topología propuesta.

Las figuras 5.a a 5.d representan los pasos se-guidos para la obtención de la segunda topología objeto de la presente invención.

La figura 6 muestra el esquema eléctrico del primer circuito objeto de la presente invención.

La figura 7 muestra el esquema del segundo circuito objeto de la presente invención.

Las figuras 8.a a 8.d representan diversas alternativas para la realización del circuito resonante.

### Descripción de la invención

El objeto de la presente invención son dos circuitos electrónicos para alimentación de lámparas de descarga para potencias comprendidas entre 85 y 400 vatios cumpliendo la normativa relativa a la emisión de armónicos de baja frecuencia. Las soluciones más comúnmente empleadas en la actualidad para la implementación de balastos electrónicos en este rango de potencias están constituidas por dos etapas: un conversor continua-continua con corrección del factor de potencia seguido de un inversor resonante en puente completo. Esta configuración precisa de un circuito de control para cada etapa y presenta un elevado número total de componentes lo cual supone un elevado precio final.

Una de las posibles soluciones para reducir el coste de los balastos electrónicos es el empleo de topologías integradas como las descritas en el anterior estado de la técnica. Estas topologías provienen de la integración de una etapa de entrada con corrección de factor de potencia y un inversor resonante. La característica común de todas ellas es que uno solo de los interruptores soporta los esfuerzos propios de la etapa de entrada más parte de los debidos al inversor resonante. Por tanto, para el rango de potencias al que se orientan los circuitos de la presente invención, resultan difícilmente aplicables debido a los elevados esfuerzos de tensión y corriente que se concentran en uno solo de los interruptores.

Los circuitos objeto de la presente invención provienen de la integración del rectificador de entrada, un convertidor reductor funcionando como etapa de corrección del factor de potencia y un inversor resonante en puente completo. Si bien las topologías básicas empleadas para la obtención de ambos circuitos son las mismas, el procedimiento empleado para su obtención y las características finales de los mismos son sustancialmente distintas.

A continuación se describe el funcionamiento y características de ambos circuitos. Para ello se realizará una breve descripción de los pasos seguidos para su obtención. Este procedimiento proporciona una imagen más clara acerca del funcionamiento que la que proporcionaría el análisis de los modos topológicos por los que atraviesa el circuito.

En primer lugar, se realiza una breve introducción a la técnica de integración de interruptores utilizada, por ser ésta uno de los puntos clave para la obtención de ambos circuitos.

La integración de etapas se ha realizado utilizando la técnica de compartir interruptores (T.-F. Wu et al, "A Systematic Illustration of the Applications of Grafted Converter Trees", International Conference on Industrial Electronics, Control and Instrumentation, 1996). El procedimiento seguido se puede resumir en lo siguiente: en un circuito cualquiera, dos interruptores unidireccionales en tensión, que tienen un terminal común y que comutan simultáneamente se pueden integrar en un único interruptor controlado y varios diodos. Las equivalencias empleadas para la ob-

tención de los circuitos de la presente invención se muestran en las figuras 1.a y 1.b.

La figura 1.a muestra el proceso de integración que hay que emplear cuando la tensión en el terminal común de ambos interruptores (punto B) puede ser únicamente negativa respecto a uno de los terminales no comunes (terminal A) y positiva respecto al otro (terminal C). En este caso los interruptores (1) y (2) pueden unirse en un solo interruptor (5) como se muestra en la figura 1.a. La corriente que ha de soportar en conducción el interruptor compartido (5) es la mayor de las corrientes que soportaban los interruptores (1) y (2) del circuito original. En cambio, la tensión que soporta en abierto el interruptor (5) es la suma de las que habrían de soportar los interruptores (1) y (2) del circuito original. Es decir, los esfuerzos de corriente que soporta el interruptor compartido con este método son similares a los que soportaban los interruptores antes de la integración, pero los esfuerzos de tensión son notablemente superiores.

La figura 1.b muestra el proceso de integración que hay que emplear cuando la tensión en el terminal común de ambos interruptores (punto B) puede ser únicamente negativa respecto a los terminales no comunes de ambos interruptores (terminales A y C). En este caso los interruptores (8) y (9) pueden integrarse en un solo interruptor (12) como se ilustra en la figura. A diferencia del caso anterior, la tensión que ha de soportar en abierto el interruptor compartido (12) es la mayor de las tensiones que soportaban los interruptores (8) y (9) del circuito original. En cambio, la corriente que soporta en conducción el interruptor (12) es la suma de las que soportaban los interruptores (8) y (9) del circuito original. Es decir, los esfuerzos de tensión que soporta el interruptor compartido son similares a los que soportaban los interruptores antes de la integración, sin embargo los esfuerzos de corriente son sensiblemente mayores. Dependiendo de las características del circuito original, puede no ser necesario añadir alguno de los diodos (13) ó (16) que se muestran en la figura 1.b.

Estos dos procedimientos para la integración de interruptores han sido empleados en la obtención de los circuitos objeto de la presente invención.

### Topología 1

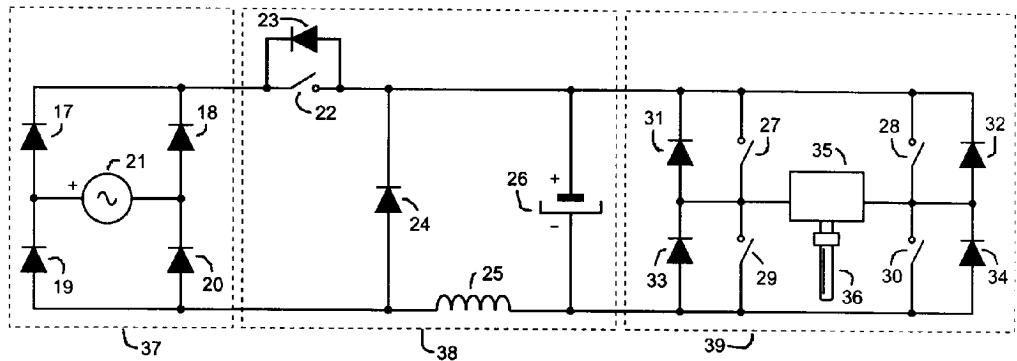

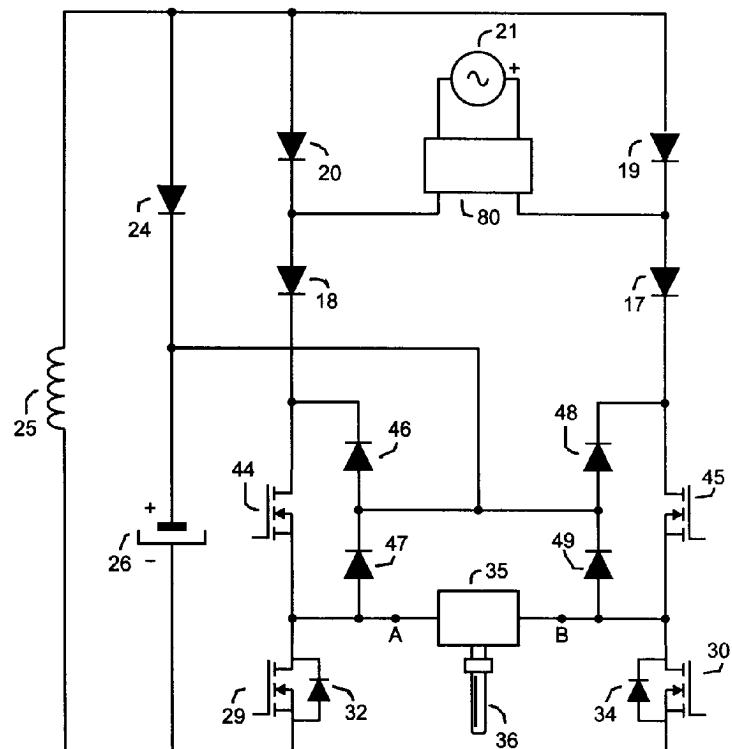

La figura 4.a muestra el esquema eléctrico del circuito empleado como base para la obtención de las dos topologías de la presente invención. El circuito está compuesto por un rectificador de entrada (37) seguido por un convertidor reductor (38) y un inversor resonante en puente completo (39).

El convertidor reductor se emplea como etapa para la corrección del factor de potencia. Las formas de onda básicas correspondientes a esta etapa se muestran en la figura 2. La figura 2.a muestra las tensiones de entrada y salida del convertidor reductor. En la figura 2.b se observa la forma de onda de la corriente por la inductancia del reductor (25). La figura 2.c muestra el valor promedio de la corriente de entrada al convertidor, es decir la corriente de entrada tras filtrar las componentes de alta frecuencia introducidas por

el ruido de conmutación. Como se puede observar en dichas figuras, el convertidor reductor trabaja únicamente en los intervalos en que la tensión de entrada es superior a la tensión de salida. Funcionando en modo de conducción discontinuo a frecuencia y ciclo de trabajo fijos se consigue una corriente de entrada al convertidor (Figura 2.c) proporcional a la diferencia entre la tensión de entrada y la tensión de salida del mismo. Por tanto, este circuito no funciona como emulador de resistencia sino que busca el cumplimiento de la normativa relativa a la emisión de armónicos de baja frecuencia con un circuito sencillo y de bajo coste.

La última etapa del circuito de la figura 4.a es un inversor resonante en puente completo formado por cuatro interruptores (27, 28, 29 y 30) y sus respectivos diodos de libre circulación (31, 32, 33 y 34) que alimentan la lámpara (36) a través de un circuito resonante (35). Para obtener una señal alterna de onda cuadrada a la entrada del circuito resonante se hace conmutar simultáneamente los interruptores (27) y (30) y los interruptores (28) y (29) con un desfase entre ambos grupos de  $180^\circ$ . Las formas de onda básicas del funcionamiento de esta etapa del circuito se muestran en la figura 3. Las figura 3.a y 3.b muestran respectivamente la tensión y corriente de entrada del circuito resonante cuando éste presenta comportamiento inductivo. La figura 3.c muestra las señales de control de los interruptores (27) y (30) y la figura 3.d las señales de control de los interruptores (28) y (29).

La figura 4.b muestra una variación del circuito anterior donde se emplean dos interruptores (40) y (41) en la etapa reductora de entrada en lugar de un interruptor único (22) como mostraba el circuito de la figura 4.a. De esta forma los esfuerzos de tensión y corriente de la etapa de entrada se reparten alternativamente entre los interruptores (40) y (41) en cada semicírculo de la tensión de entrada (21). Cuando la tensión de entrada (21) es positiva trabaja el interruptor (40) y cuando es negativa el interruptor (41). Además, esto es así aún cuando los interruptores (40) y (41) no comuten de forma simultánea. Se puede por tanto hacer conmutar estos interruptores de forma sincronizada con los del lado superior del puente completo (27) y (28), como se indica mediante líneas de puntos en la figura 4.b. De esta forma, los interruptores (40) y (28) por una parte y (41) y (27) por otra, se pueden integrar en dos únicos interruptores (44) y (45) dando lugar al circuito que se muestra en la figura 4.c. Este circuito corresponde a la primera topología objeto de la presente invención.

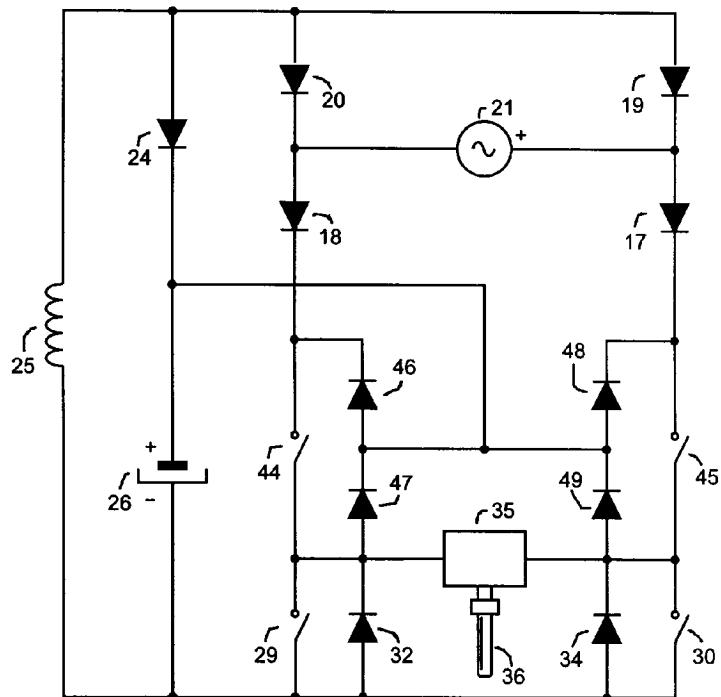

En la figura 6 se muestra un circuito equivalente al mostrado en la figura 4.c incluyendo el filtro de entrada. Atendiendo al esquema de la figura 6 el circuito propuesto está compuesto por un primer filtro de entrada (80) con uno de sus terminales conectados al ánodo de un primer diodo (18) y al cátodo de un segundo (20), y el otro terminal conectado a su vez con el ánodo de un tercer diodo (17) y al cátodo de un cuarto (19); los ánodos de los diodos (19) y (20) se encuentran unidos entre sí y también con el ánodo un diodo (24) y uno de los terminales de la inductancia

(25); el otro terminal de la inductancia (25) se encuentra a su vez conectado al terminal negativo del condensador principal del convertidor (26), el cual tiene a su vez el terminal positivo conectado con el cátodo del diodo (24); el cátodo del diodo (18) conecta con el drenador de un transistor MOSFET de canal N (44), el cual se encuentra en serie con un segundo transistor MOSFET (29) también de canal N; en paralelo con el transistor (44) se encuentran dos diodos conectados en serie (47) y (46), el punto medio de estos diodos se encuentra conectado con el terminal positivo del condensador principal (26); el cátodo del diodo (17) conecta con el drenador de un tercer transistor MOSFET de canal N (45), el cual se encuentra en serie con otro transistor MOSFET de canal N (30); en paralelo con el transistor (45) se encuentran dos diodos conectados en serie (48) y (49), el punto medio de estos diodos se encuentra conectado a su vez con el terminal positivo del condensador principal (26); por otra parte, al terminal negativo de dicho condensador se encuentra conectado con los surtidores de los transistores (29) y (30); en paralelo con estos transistores se dispone de dos diodos (32) y (34), si bien se pueden aprovechar los diodos parásitos de los transistores MOSFET; finalmente, los drenadores de los transistores (29) y (30) corresponden con los terminales de salida del convertidor A y B al cual se conecta la lámpara (36) a través de un circuito resonante (35).

Las características básicas de esta topología son:

- Presenta una característica de entrada equivalente a la de un convertidor reductor funcionando en modo de conducción discontinuo.

- La característica de salida corresponde a la de un inversor resonante en puente completo.

- Las tensiones que soportan los interruptores inferiores del puente (29) y (30) es igual a la tensión de salida del convertidor reductor (26), pero la tensión en los interruptores compartidos (44) y (45) es la suma de esta y la tensión de entrada al convertidor (21). Sin embargo, para el rango de tensiones en uso actualmente en la Comunidad Europea, los cuatro interruptores pueden realizarse empleando dispositivos semiconductores de bajo coste.

## Topología 2

A continuación se describe el funcionamiento y características de la segunda topología objeto de la presente invención mediante el análisis de los pasos seguidos para su obtención mediante la integración de una etapa de tipo reductor con un inversor en puente completo.

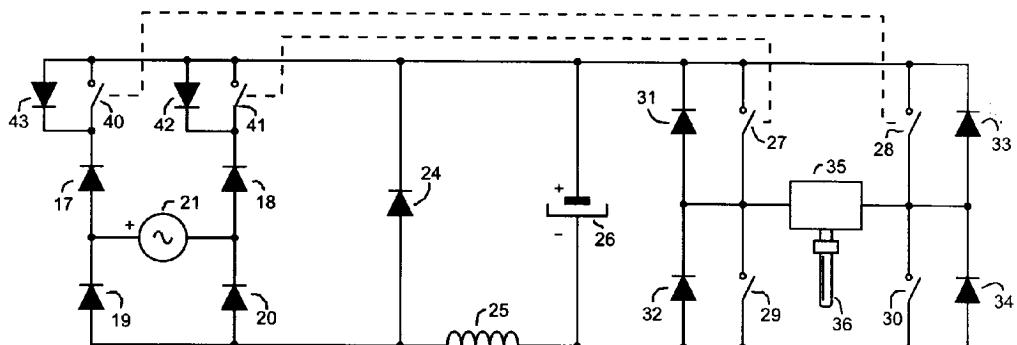

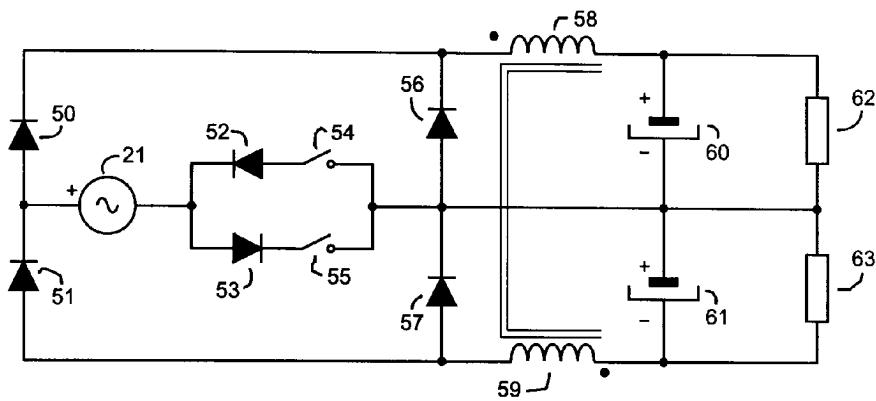

Los circuitos empleados como base para la obtención de esta topología se muestran en las figuras 5.a y 5.b. El circuito que se muestra en la figura 5.a es una variante de un convertidor reductor que puede usarse para repartir los esfuerzos de conmutación entre dos interruptores (54) y (55). Este circuito equivale a dos convertidores reductores: uno que trabaja únicamente durante el semicírculo positivo de la tensión de entrada (21) y que alimenta la carga (62) y otro que trabaja en los semicírculos negativos y alimenta la carga (63). De esta forma, los interruptores (54) y (55) solamente soportan esfuerzo durante un semicírculo de

la tensión de entrada. Otra de las características de este circuito es que las inductancias (58) y (59) se pueden acoplar entre sí y devanarse empleando un único núcleo magnético. De esta forma, los diodos (56) y (57) pueden ser eliminados del circuito ya que los diodos (50) y (51) proporcionan un camino alternativo para la descarga del núcleo magnético empleado para construir las inductancias (58) y (59).

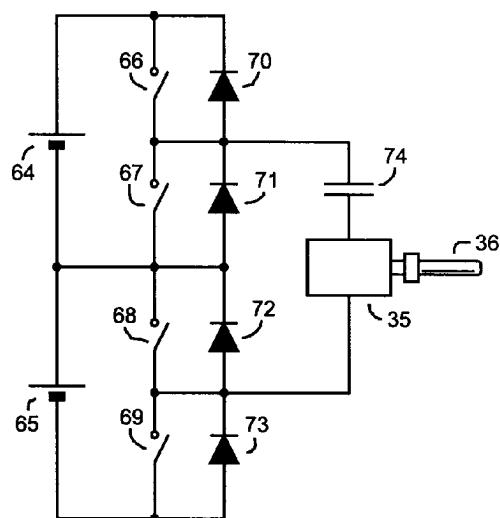

El circuito de la figura 5.a no puede ser utilizado para la alimentación de un puente completo normal pero sí para un puente completo asimétrico como el que se muestra en la figura 5.b. El funcionamiento normal de este circuito se obtiene cuando se hacen conmutar simultáneamente los interruptores (66) y (69) y, con un desfase de  $180^\circ$  respecto a estos, los interruptores (67) y (68). De esta forma la tensión de salida varía entre cero y la suma de las tensiones de las fuentes (64) y (65). En un puente completo normal la tensión de salida puede ser positiva o negativa, en cambio en un puente completo asimétrico la tensión de salida es siempre positiva. Por este motivo, es necesario incorporar algún elemento que filtre la componente de continua como es el condensador (74). No obstante, los esfuerzos en los interruptores de un puente completo asimétrico son equivalentes a los de un puente completo normal.

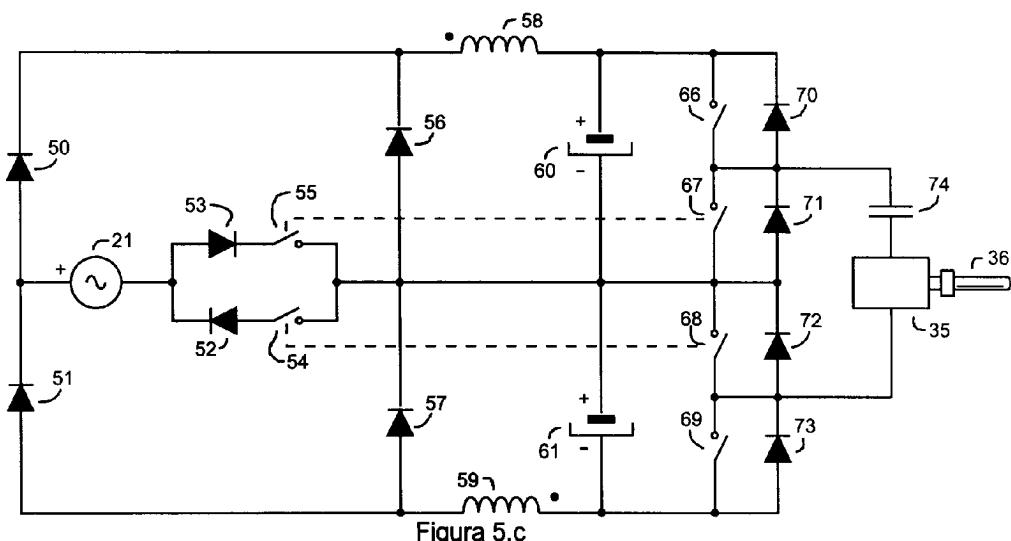

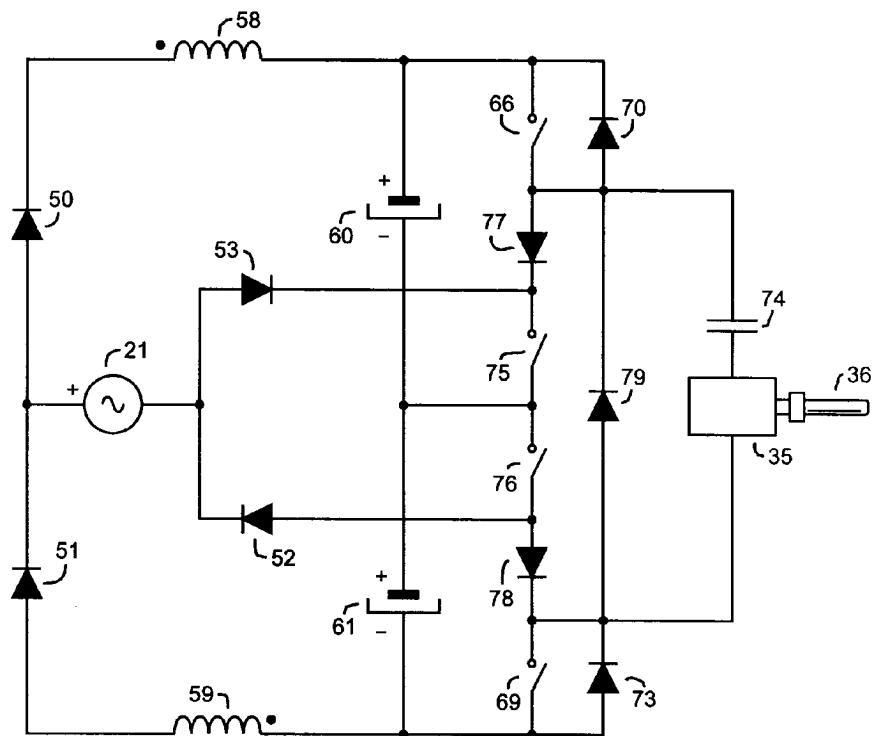

Combinando el convertidor mostrado en la figura 5.a con el inversor asimétrico de la figura 5.b se obtiene el circuito de la figura 5.c. Como se puede observar, los interruptores (55) y (67) tienen un terminal común, si se les hace conmutar de forma sincronizada pueden ser integrados en un solo interruptor. De forma análoga se puede proceder con los interruptores (54) y (68); el circuito que se obtiene de este modo es el mostrado en la figura 5.d. En este circuito se han suprimido también los diodos innecesarios que se obtienen después de integración. Este circuito se corresponde con la segunda topología objeto de la presente invención.

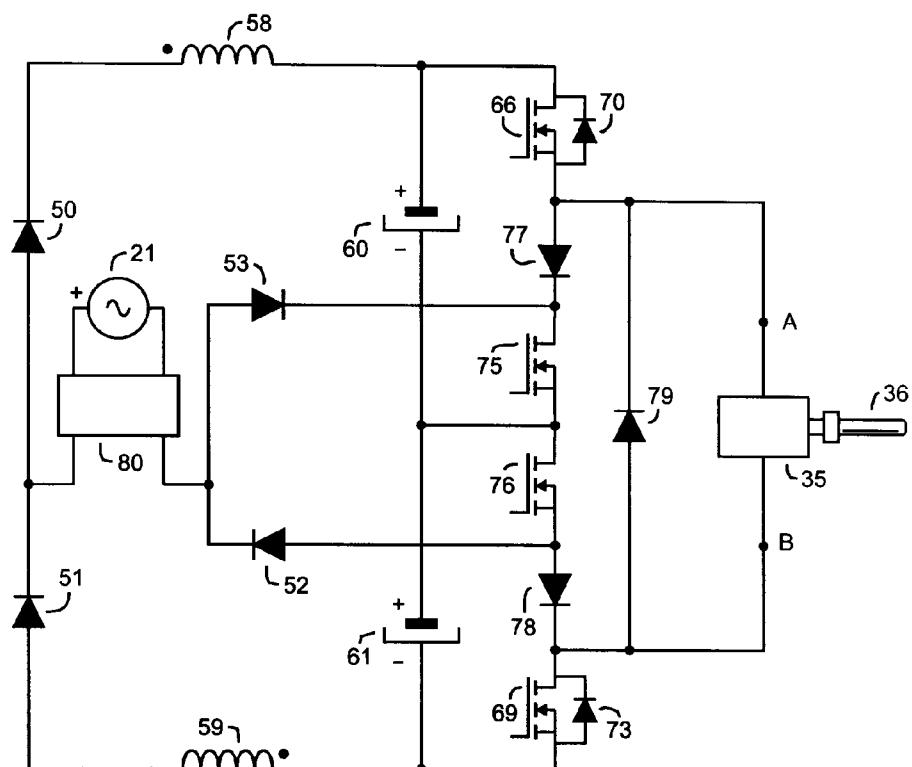

En la figura 7 se muestra un circuito equivalente al mostrado en la figura 5.d incluyendo el filtro de entrada (80). Atendiendo a la figura 7, el circuito propuesto está compuesto por un primer filtro (80) con uno de sus terminales conectados al ánodo de un primer diodo (50) y al cátodo de un segundo (51), y el otro terminal conectado con el ánodo de un tercer diodo (53) y al cátodo de un cuarto (52); el cátodo del diodo (50) está conectado a su vez con uno de los terminales de una inductancia (58); el otro terminal de dicha inductancia está conectado con el terminal positivo del condensador (60), el terminal negativo de este condensador se encuentra conectado con el terminal positivo de un segundo condensador (61); y por otra parte, el ánodo del diodo (51) se encuentra conectado con uno de los terminales de la inductancia (59), el otro terminal de esta inductancia está conectado al terminal negativo del condensador (61); además, las inductancias (59) y (58) se pueden encontrar o no acopladas magnéticamente; por otra parte, en paralelo con el condensador (60) se encuentran conectados un primer transistor MOSFET (66) seguido de un diodo (77) y un segundo transistor MOSFET (75)

los tres en serie, de forma tal que el drenador del transistor (66) está conectado al terminal positivo del condensador (60), el surtidor con el ánodo del diodo (77), el cual tiene a su vez el cátodo conectado con el drenador del segundo transistor (75), el surtidor de (75) está conectado al terminal negativo del condensador (60); los cátodos de los diodos (53) y (77) también están conectados entre sí; en paralelo con el condensador (61) se encuentran conectados un tercer transistor MOSFET (76) seguido de un diodo (78) y un cuarto transistor MOSFET (69) los tres en serie, de forma tal que el drenador del transistor (76) está conectado al terminal positivo del condensador (61), el surtidor con el ánodo del diodo (78), el cual tiene a su vez el cátodo conectado con el drenador del transistor (69), el surtidor de (69) está conectado al terminal negativo del condensador (61); los ánodos de los diodos (52) y (78) también están conectados entre sí; en paralelo con los transistores (66) y (69) se dispone de dos diodos (70) y (73), si bien pueden aprovecharse los diodos parásitos de los transistores MOSFET; finalmente, el ánodo del diodo (77) y el cátodo del diodo (78) constituyen los terminales de salida del convertidor A y B entre los cuales se conecta el diodo de libre circulación (79) y el circuito resonante (35) empleado para alimentar la lámpara (36).

Las características básicas de esta topología son:

- Presenta una característica de entrada equivalente a la de un convertidor reductor funcionando en modo de conducción discontinua.

- La característica de salida corresponde a la de un inversor resonante en puente completo asimétrico.

- Las tensiones que soportan los interruptores inferior y superior del puente asimétrico (69) y (66) son iguales a las tensiones en los condensadores (61) y (60) respectivamente, es decir son iguales a las tensiones de salida de cada semi-etapa del convertidor reductor. La tensión máxima que soportan los interruptores compartidos (67) y (68) coincide con el valor de pico de la tensión de entrada del convertidor (21) y la corriente que circula a través de ellos es la suma de la correspondiente al inversor y la correspondiente al reductor únicamente durante un semiciclo de la tensión de entrada.

Dependiendo de las características del circuito de control utilizado y del tipo de protecciones que se empleen, puede resultar más sencillo optimizar el rendimiento y coste de una u otra de las topologías descritas.

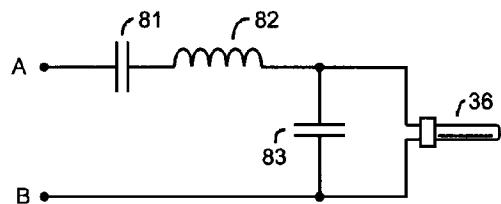

Para las dos topologías descritas anteriormente existen varias configuraciones válidas para implementar el circuito resonante (35). A modo de ejemplo, en la figura 8.a se incluye la configuración LCC serie - paralelo que es una de las más comúnmente empleadas. Esta está compuesta por un condensador (81) en serie con la inductancia resonante (82) que a su vez está en serie con el paralelo del condensador (83) y la lámpara (36).

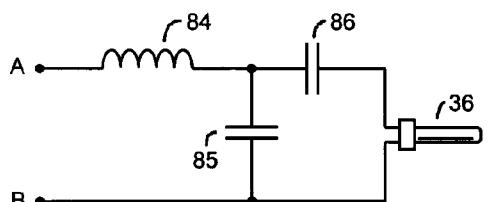

En la figura 8.b se muestra una configuración alternativa del circuito resonante. Este circuito se denomina tanque LCC paralelo- serie. Este está compuesto por una inductancia (84) seguido del

conjunto formado por el paralelo de un condensador (85) y de la combinación formada por la lámpara (36) en serie con un segundo condensador (86).

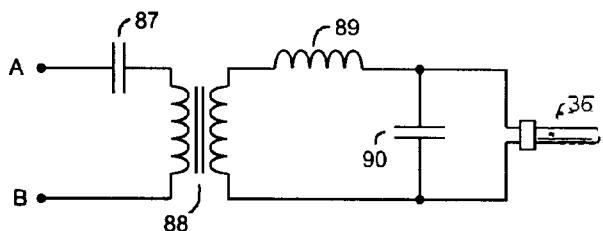

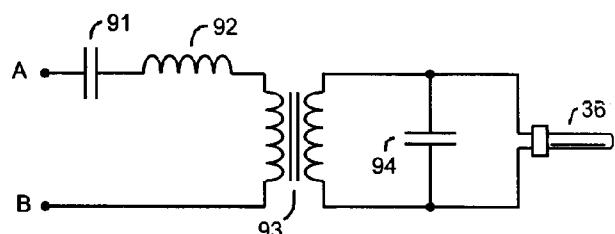

Las figuras 8.c y 8.d muestran dos configuraciones con aislamiento para la implementación del tanque resonante. La principal diferencia entre ambas son los esfuerzos de tensión que soportan los devanados del transformador de aislamiento durante el transitorio de cebado. El circuito de la figura 8.c está constituido por un condensador (87) en serie con el primario de un transformador (88); estando el secundario de dicho transformador conectado a una inductancia (89) seguida por un condensador (90) en paralelo con la lámpara (36). El circuito de la figura 8.d está constituido por un condensador (91) en serie con una inductancia (92) y el primario de un transformador (93); estando el secundario de dicho transformador conectado al conjunto formado por el condensador (94) y la lámpara (36) en paralelo. En este último circuito, los esfuerzos de tensión en los devanados del transformador son más altos que en el circuito de la figura 8.c debido a que el secundario del transformador se encuentra en paralelo con la lámpara.

5

10

15

20

25

30

35

40

45

50

55

60

65

En las descripciones de los circuitos correspondientes a las topologías 1 y 2 se han empleado transistores MOSFET, si bien ambos circuitos pueden ser implementados utilizando transistores bipolares o IGBTs.

### Ventajas de la invención

La principal ventaja de las topologías objeto de la presente invención es su menor coste. El tipo de soluciones empleadas actualmente para el diseño de balastos electrónicos para lámparas de potencia comprendida entre 85 y 400 vatios, consiste en utilizar dos etapas en cascada: un convertidor de entrada que proporciona un elevado factor de potencia y un inversor resonante en puente completo que alimenta a la lámpara. El número total de componentes que presentan este tipo de configuraciones es muy grande lo que supone un elevado precio de los balastos hechos de esta forma. Los circuitos de la invención presentan un número inferior de componentes, siendo además posible una mejor optimización de los esfuerzos en los dispositivos semiconductores. Esto permite obtener balastos electrónicos de menor coste manteniendo, o incluso mejorando, la eficiencia de las soluciones más comúnmente empleadas actualmente.

## REIVINDICACIONES

1. Un circuito electrónico para la alimentación de lámparas de descarga con corrección activa del factor de potencia basado en una topología de una sola etapa, **caracterizado** porque genera una señal de alta frecuencia para alimentar una lámpara de descarga (36) a partir de la red alterna de energía (21), tal y como se muestra en la figura 6. Estando dicho circuito compuesto por un primer filtro (80) con uno de sus terminales conectados al ánodo de un primer diodo (18) y al cátodo de un segundo (20), y el otro terminal conectado a su vez con el ánodo de un tercer diodo (17) y al cátodo de un cuarto (19); los ánodos de los diodos (19) y (20) se encuentran unidos entre sí y también con el ánodo un diodo (24) y uno de los terminales de la inductancia (25); el otro terminal de la inductancia (25) se encuentra a su vez conectado al terminal negativo del condensador principal del convertidor (26), el cual tiene a su vez el terminal positivo conectado con el cátodo del diodo (24); el cátodo del diodo (18) conecta con el drenador de un transistor MOSFET de canal N (44), el cual se encuentra en serie con un segundo transistor MOSFET (29) también de canal N; en paralelo con el transistor (44) se encuentran dos diodos conectados en serie (47) y (46), el punto medio de estos diodos se encuentra conectado con el terminal positivo del condensador principal (26); el cátodo del diodo (17) conecta con el drenador de un tercer transistor MOSFET de canal N (45), el cual se encuentra en serie con otro transistor MOSFET de canal N (30); en paralelo con el transistor (45) se encuentran dos diodos conectados en serie (48) y (49), el punto medio de estos diodos se encuentra conectado a su vez con el terminal positivo del condensador principal (26); por otra parte, al terminal negativo de dicho condensador se encuentra conectado con los surtidores de los transistores (29) y (30); en paralelo con estos transistores se dispone de dos diodos (32) y (34), si bien se pueden aprovechar los diodos parásitos de los transistores MOSFET, finalmente, los drenadores de los transistores (29) y (30) corresponden con los terminales de salida del convertidor A y B al cual se conecta la lámpara (36) a través de un circuito resonante (35); la configuración del circuito resonante se muestra en la figura 8.a, éste está compuesto por un condensador (81) en serie con una inductancia (82) que a su vez está en serie con el paralelo del condensador (83) y la lámpara (36).

2. Un circuito electrónico para la alimentación de lámparas de descarga con corrección activa del factor de potencia basado en una topología de una sola etapa, **caracterizado** porque genera una señal de alta frecuencia para alimentar una lámpara de descarga (36) a partir de la red alterna de energía (21), tal y como se muestra en la figura 6. Estando dicho circuito compuesto por un primer filtro (80) con uno de sus terminales conectados al ánodo de un primer diodo (50) y al cátodo de un segundo (51), y el otro terminal conectado con el ánodo de un tercer diodo (53) y al cátodo de un cuarto (52); el cátodo del diodo (50) está conectado a su vez con uno de los terminales de una inductancia (58); el otro terminal de

dicha inductancia está conectado con el terminal positivo del condensador (60), el terminal negativo de este condensador se encuentra conectado con el terminal positivo de un segundo condensador (61); y por otra parte, el ánodo del diodo (51) se encuentra conectado con uno de los terminales de la inductancia (59), el otro terminal de esta inductancia está conectado al terminal negativo del condensador (61); además, las inductancias (59) y (58) se pueden encontrar o no acopladas magnéticamente; por otra parte, en paralelo con el condensador (60) se encuentran conectados un primer transistor MOSFET de canal N (66) seguido de un diodo (77) y un segundo transistor MOSFET (75) los tres en serie, de forma tal que el drenador del transistor (66) está conectado al terminal positivo del condensador (60), el surtidor con el ánodo del diodo (77), el cual tiene a su vez el cátodo conectado con el drenador del segundo transistor (75), el surtidor de (75) esta conectado al terminal negativo del condensador (60); los cátodos de los diodos (53) y (77) también están conectados entre sí; en paralelo con el condensador (61) se encuentran conectados un tercer transistor MOSFET de canal N (76) seguido de un diodo (78) y un cuarto transistor MOSFET (69) los tres en serie, de forma tal que el drenador del transistor (76) está conectado al terminal positivo del condensador (61), el surtidor con el ánodo del diodo (78), el cual tiene a su vez el cátodo conectado con el drenador del transistor (69), el surtidor de (69) esta conectado al terminal negativo del condensador (61); los ánodos de los diodos (52) y (78) también están conectados entre sí; en paralelo con los transistores (66) y (69) se dispone de dos diodos (70) y (73), si bien pueden aprovecharse los diodos parásitos de los transistores MOSFET; finalmente, el ánodo del diodo (77) y el cátodo del diodo (78) constituyen los terminales de salida del convertidor A y B entre los cuales se conecta el diodo de libre circulación (79) y el circuito resonante (35) empleado para alimentar la lámpara (36); la configuración del circuito resonante se muestra en la figura 8.a, éste está compuesto por un condensador (81) en serie con una inductancia (82) que a su vez está en serie con el paralelo del condensador (83) y la lámpara (36).

3. Un circuito, según las reivindicaciones anteriores, **caracterizado** porque el circuito resonante (35) está constituido por una inductancia (84) seguida por un condensador (85) el cual tiene conectado en paralelo otro condensador (86) en serie con la lámpara tal y como se muestra en la figura 8.b.

4. Un circuito, según las reivindicaciones 1 y 2, **caracterizado** porque el circuito resonante (35) está constituido por un condensador (87) en serie con el primario de un transformador (88); estando el secundario de dicho transformador conectado a una inductancia (89) seguida por un condensador (90) en paralelo con la lámpara (36) tal y como se muestra en la figura 8.c.

5. Un circuito, según las reivindicaciones 1 y 2, **caracterizado** porque el circuito resonante (35) está constituido por un condensador (91) en serie con una inductancia (92) y el primario de un transformador (93); estando el secundario de

dicho transformador conectado a un condensador (94) y a la lámpara (36) en paralelo, tal y como se muestra en la figura 8.d.

6. Un circuito, según las reivindicaciones anteriores, **caracterizado** porque cualquiera de los interruptores es un transistor bipolar o un IGBT.

5

10

15

20

25

30

35

40

45

50

55

60

65

Figura 1.a

Figura 1.b

Figura 2

Figura 3

# ES 2 180 386 B1

Figura 4.a

Figura 4.b

Figura 4.c

Figura 5.a

Figura 5.b

Figura 5.c

Figura 5.d

Figura 6

Figura 7

Figura 8.a

Figura 8.c

Figura 8.b

Figura 8.d

OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

- (11) ES 2 180 386

(21) N° de solicitud: 200001982

(22) Fecha de presentación de la solicitud: 31.07.2000

(32) Fecha de prioridad:

## INFORME SOBRE EL ESTADO DE LA TÉCNICA

(51) Int. Cl.7: H05B 41/288

### DOCUMENTOS RELEVANTES

| Categoría | Documentos citados                                                                   | Reivindicaciones afectadas |

|-----------|--------------------------------------------------------------------------------------|----------------------------|

| A         | WO 9722232 A1 (PHILIPS ELECTRONICS N.V.; PHILIPS NORDEN AB)<br>19.06.1997            |                            |

| A         | BASE DE DATOS PAJ en EPOQUE.<br>JP 07-220887 A (EYE LIGHTING SIST. CORP.) 18.08.1995 |                            |

#### Categoría de los documentos citados

X: de particular relevancia

Y: de particular relevancia combinado con otro/s de la misma categoría

A: refleja el estado de la técnica

O: referido a divulgación no escrita

P: publicado entre la fecha de prioridad y la de presentación de la solicitud

E: documento anterior, pero publicado después de la fecha de presentación de la solicitud

#### El presente informe ha sido realizado

para todas las reivindicaciones

para las reivindicaciones nº:

|                                                |                                    |               |

|------------------------------------------------|------------------------------------|---------------|

| Fecha de realización del informe<br>17.12.2002 | Examinador<br>J. Botella Maldonado | Página<br>1/1 |

|------------------------------------------------|------------------------------------|---------------|