OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 130 997**

(21) Número de solicitud: 009701080

(51) Int. Cl.<sup>6</sup>: H04R 25/00

(12)

## PATENTE DE INVENCION

B1

- (22) Fecha de presentación: **20.05.1997**

(43) Fecha de publicación de la solicitud: **01.07.1999**

Fecha de concesión: **29.12.1999**

(45) Fecha de anuncio de la concesión: **16.02.2000**

(45) Fecha de publicación del folleto de patente:

**16.02.2000**

- (73) Titular/es: **Universidad de Málaga

El Ejido s/n, Edf. Rectorado

29071 Málaga, ES**

(72) Inventor/es: **Gago Bohórquez, Alfonso;

Hidalgo López, José Antonio;

Tejero Calado, Juan Carlos;

Daza Márquez, Alberto;

Oballe Peinado, Oscar;

Fernández Ramos, José;

Martín Vázquez, Manuel Jesús;

González Spinola, Carlos y

Urquiza de la Rosa, Rafael**

(74) Agente: **No consta**

(54) Título: **Procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes y procesador digital para la realización del mismo.**

(57) Resumen:

Procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes y procesador digital para la realización del mismo.

Procedimiento de tratamiento de señales de audio de 32 bandas con compresión de amplitudes, del tipo de los que se utilizan para compensar la señal hablada a personas con pérdidas neurosensoriales con el objeto de aumentar su inteligibilidad, y procesador digital para la realización de dicho procedimiento, a utilizar preferentemente en la industria dedicada a la fabricación de prótesis auditivas digitales de ayuda a individuos con pérdidas acústicas, comprendiendo dicho procedimiento las etapas de:

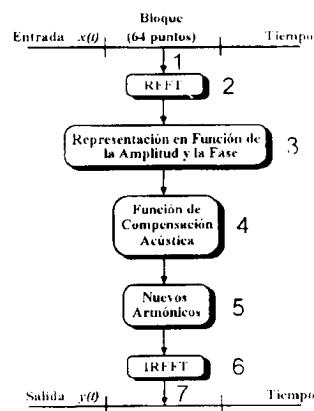

- recepción (1) de la señal en el tiempo  $x(t)$  de entrada en bloques de 64 puntos;

- obtención de la representación espectral de cada uno de dichos bloques de señal en el tiempo mediante la Transformada Rápida de Fourier (FFT) (2);

- representación exponencial (3) de las componentes en frecuencia obtenidas en dicha representación espectral;

- aplicación de una función de compensación acústica (4) aplicada sobre la amplitud de cada uno de los armónicos obtenidos en dicha representación exponencial; y

– sintetización de dicha señal espectral modificada (5) mediante la Transformada Inversa Rápida de Fourier (IFFT)(6), para obtener la señal en el tiempo de salida  $y(t)$ .

Fig. 1

ES 2 130 997 B1

Aviso: Se puede realizar consulta prevista por el artº 37.3.8 LP.

## DESCRIPCION

Procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes y procesador digital para la realización del mismo.

El objeto de la presente invención se refiere, como su título indica, a un procedimiento de tratamiento de señales de audio de 32 bandas con compresión de amplitudes, del tipo de los que se utilizan para compensar la señal hablada a personas con pérdidas neurosensoriales con el objeto de aumentar su inteligibilidad, así como a un procesador digital para la realización de dicho procedimiento, a utilizar preferentemente en la industria dedicada a la fabricación de prótesis auditivas digitales de ayuda a individuos con pérdidas acústicas, que presenta unas ventajas importantes sobre los medios utilizados actualmente con este fin.

En la actualidad se conocen diferentes problemas causantes de pérdidas auditivas, entre los que se pueden resaltar dos como los más importantes, como son aquellos problemas debidos a la degradación de la energía, acústica que recibe la ceclea, y los problemas debidos a pérdidas neurosensoriales originadas por problemas en la ceclea y/o en el nervio auditivo.

En el primer caso, esto es, aquellos problemas debidos a la degradación de la energía acústica que recibe la ceclea, la pérdida auditiva puede ser modelada de una forma lineal. Esta característica permite que las prótesis auditivas tradicionales trabajen de una forma eficiente para corregir este tipo de problemas, en tanto que realizan una amplificación lineal en todo el rango de frecuencias.

Sin embargo, cuando los problemas se deben a pérdidas auditivas neurosensoriales, los sujetos que las padecen poseen un rango dinámico estrecho, debido al fenómeno conocido como "recruitment" (o reclutamiento), las prótesis auditivas basadas en una amplificación lineal, no contribuyen eficazmente a mejorar la ausencia de inteligibilidad de la voz, en tanto que la amplificación lineal puede salirse fácilmente del rango dinámico del paciente. Este tipo de prótesis tradicionales recortan la señal que excede el intervalo de audición del individuo, lo que provoca la pérdida de inteligibilidad. Por todo ello, con el objeto de compensar adecuadamente las pérdidas neurosensoriales, el procesado debe ser un procesado no lineal y/o variante en el tiempo.

Actualmente se conocen en el mercado diferentes tipos de prótesis auditivas que se pueden englobar básicamente en dos grupos como son las prótesis auditivas analógicas y las prótesis auditivas digitales. Las prótesis auditivas analógicas realizan una ecualización de la señal en el tiempo, tratando individualmente las frecuencias graves, medias y agudas. Por su parte, las prótesis auditivas digitales realizan una representación en la frecuencia de la señal, utilizando cuatro bancos de filtros digitales, por lo que tratan un grupo de frecuencias de la misma manera, realizando una ecualización lineal de la señal, sin comprimirla.

Con el objeto de subsanar eficazmente las carencias que presentan las prótesis digitales auditivas existentes en la actualidad para resolver fundamentalmente los problemas debidos a pérdidas auditivas neurosensoriales, se ha desarrollado el procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes y el procesador digital para la realización de dicho procedimiento objeto de la presente invención.

5

10

15

20

25

30

35

40

45

50

60

65

El objetivo de la presente invención se centra en el procesado de las representaciones espectrales obtenidas por medio de la Transformada Rápida de Fourier (FFT), tratando de reconstruir la señal espectral dentro del rango dinámico del paciente con pérdidas neurosensoriales mediante una función de compensación.

Un primer objeto de la presente invención se refiere al desarrollo de un procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes, del tipo de los que se utilizan para compensar la señal hablada a personas con pérdidas neurosensoriales con el objeto de aumentar su inteligibilidad.

Un segundo objeto de la presente invención se refiere a un procesador digital para la realización de dicho procedimiento, a utilizar preferentemente en la industria dedicada a la fabricación de prótesis auditivas digitales de ayuda a individuos con pérdidas acústicas.

Más concretamente, el procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes objeto de la presente invención comprende:

- la recepción de la señal en el tiempo  $x(t)$  de entrada en bloques de 64 puntos;

- la obtención de la representación espectral de cada uno de dichos bloques de señal en el tiempo mediante la Transformada Rápida de Fourier (FFT),

- la representación exponencial de las componentes en frecuencia obtenidas en dicha representación espectral

$$S_K = A_K e^{j\theta_K} \quad (1.1)$$

donde  $A_K$  representa la amplitud y  $\theta_K$  representa la fase;

- la aplicación de una función de compensación acústica aplicada sobre la amplitud de cada uno de los armónicos obtenidos en dicha representación exponencial, obtenida a partir de la relación:

$$\frac{\alpha^i_K - P_n}{D_n - \alpha^i_K} = \frac{\alpha^o_K - P_p}{D_p - \alpha^o_K} \quad (2.1)$$

representando  $\alpha^i_K$  y  $\alpha^o_K$  la amplitud en decibelios de los armónicos ( $A^i_K$ ) y ( $A^o_K$ ), a modificar respectivamente,  $P_n$  y  $D_n$  los niveles de percepción y dolor para un oyente normal,  $P_p$  y  $D_p$  los niveles de percepción y dolor para un oyente con pérdidas, obteniendo unos nuevos armónicos modificados en amplitud dados por:

$$A^o_K = K_1 (A^i_K)^{K_2} \quad (3.1)$$

manteniendo la fase original, y donde  $K_1$  y  $K_2$  son constantes derivadas de los niveles de percepción y dolor del individuo; y

– la sintetización de dicha señal espectral modificada mediante la Transformada Inversa Rápida de Fourier (IFFT), para obtener la señal en el tiempo de salida  $y(t)$ .

Además de las operaciones anteriormente descritas, el procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes comprende preferentemente un sencillo control de ruido apto para la eliminación de sonidos molestos en determinados ambientes.

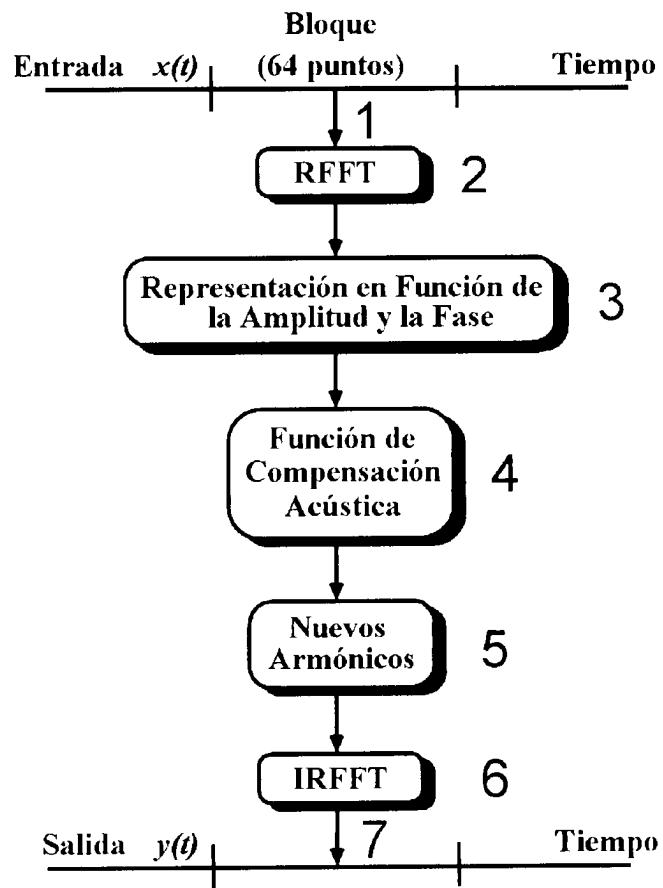

Tal y como se ha descrito anteriormente, un segundo objeto de la presente invención se refiere a un procesador digital para la realización del procedimiento anteriormente descrito, constituido por un circuito que comprende tres módulos funcionales como son:

- un bloque de entrada/salida, apto para introducir los datos desde un conversor analógico a digital (conversor A/D) de entrada y para entregar en su salida los datos tratados a un conversor digital a analógico (conversor D/A),

- un bloque que realiza la transformada rápida de Fourier, denominado de aquí en adelante *bloque FFT*, apto para realizar la transformada rápida de Fourier directa e inversa sobre los datos introducidos a través de dicho bloque de entrada/salida; y

- un bloque de modificación de armónicos, apto para realizar una operación de compresión sobre los armónicos obtenidos una vez realizada la transformada directa de Fourier sobre los datos introducidos mediante dicho bloque FFT.

Más concretamente, el bloque de entrada/salida de dicho procesador comprende:

- una cola de entrada/salida, preferentemente una cola FIFO de datos, constituida por una memoria RAM, apta para almacenar los datos de entrada hasta completar un marco a tratar así como para suministrar al exterior los resultados modificados, con dos puertos de lectura/escritura completamente independientes, y un conjunto de contadores;

- circuitos de comunicación con el conversor, que constan de dos registros de desplazamiento, aptos para, respectivamente, la conversión serie-paralelo de los datos serie provenientes del conversor A/D para su posterior entrega a la cola de entrada/salida, y para la conversión paralelo-serie de los datos paralelo provenientes de la cola de entrada/salida al conversor D/A, y apto para producir una señal de fin de comunicación para indicar que el dato de entrada está estable y se puede volcar un nuevo dato de salida;

- un bloque de programación del conversor, apto para fijar el valor de los registros responsables de cambiar la frecuencia de muestreo de la señal analógica; y

- un control de ruido, apto para realizar la media de los valores que forman un marco FFT.

La memoria RAM de dicho bloque de entrada/salida se dimensiona preferentemente para almacenar 64 palabras de 14 bits, estando dada la longitud de palabra (14 bits) por la resolución del conversor del entrada.

Uno de dichos puertos y su contador de dicha cola de entrada/salida es utilizado exclusivamente por registros serie a paralelo, apto para

leer los datos modificados en dicho bloque de modificación y enviar éstos a dicho conversor D/A del bloque de entrada/salida, así como para escribir los datos nuevos muestreados por el conversor A/D de dicho bloque de entrada/salida, intercambiándose ambos datos en la posición que indica dicho contador en ese instante.

El segundo de dichos puertos y su contador de dicha cola de entrada/salida es utilizado para realizar el intercambio de datos con el bloque FFT, apto para leer y escribir datos durante la etapa de carga, entendida como aquella etapa que comprende el volcado de los datos modificados residentes en la memoria de trabajo hacia la cola de entrada/salida de dicho bloque de entrada/salida y la escritura en memoria de los datos nuevos obtenidos en dicha cola. El intercambio de dichos datos entre la cola de entrada/salida y la memoria se realiza preferentemente uno a uno.

La programación de dicho bloque de programación del conversor se realiza preferentemente antes de la puesta en marcha del circuito.

El bloque FFT del procesador para la realización del procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes, comprende:

- una memoria RAM de doble puerto, apta para almacenar los datos sobre los que se trabaja mientras se están realizando las transformadas de Fourier directa e inversa, así como la modificación de los armónicos;

- un módulo de cálculo denominado de aquí en adelante *módulo mariposa* que comprende la mayor parte de bloques de cálculo como son dos sumadores, dos restadores, un multiplicador, un sumador/restador, dos complementadores a 2 y lógica de control;

- un módulo de generación de senos y cosenos;

- una cola FIFO de ordenación de datos, apta para reorganizar los datos de salida de dicho módulo mariposa para su escritura en dicha memoria RAM; y

- lógica de control.

La dimensión de dicha memoria RAM de doble puerto es preferentemente de 16 x 64. El ancho de cada dato es de 16 bits, en lugar de los 14 bits que poseen las palabras que provienen del conversor, con el objeto de introducir dos bits adicionales que extenderán la longitud de la palabra para mejorar la precisión de los cálculos que se efectúan con aritmética entera.

Asimismo, el bloque de modificación de armónicos del procesador para la realización del procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes, comprende circuitería apta para la implementación de dicha función de compensación acústica como son:

- un módulo de cálculo del módulo del armónico correspondiente;

- un módulo de conversión de escala lineal a escala logarítmica;

- medios de almacenamiento aptos para almacenar los datos particulares del paciente, constituidos preferentemente por una memoria RAM, una memoria RAM estática, una memoria EPROM o similares;

– medios para aplicar la compresión del armónico, consistente preferentemente en la multiplicación del módulo del armónico en escala logarítmica por un factor de compresión comprendido entre cero y uno y la suma de una constante, dependiendo tanto el factor de compresión como la constante de la frecuencia del armónico que se está tratando; y

– un módulo de conversión de escala logarítmica a escala lineal.

Cabe destacar que la descomposición de la señal de audio en 32 bandas es una descomposición óptima tanto desde el punto de vista fisiológico como del diseño microelectrónico ya que permite una gran fineza en la descripción de la forma de la deficiencia auditiva y por encima de este valor no se obtienen resultados mejores. Por otra parte, desde el punto de vista microelectrónico es muy conveniente el desarrollo de un algoritmo para una FFT que sea potencia de 2 ya que esto facilita tanto la generación de direcciones como las operaciones matemáticas a realizar. Además al ser solo 64 el número de datos a procesar para la FFT ésta no necesita demasiada memoria de almacenamiento, ni circuitos digitales en punto flotante para la corrección de errores de redondeo ya que, el número de etapas de la FFT es solo de 6.

De todo lo anteriormente descrito se deducen fácilmente las ventajas aportadas por el procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes, así como por el procesador digital para la realización de dicho procedimiento. Mediante dicho procedimiento se ofrece un tratamiento de señal adecuado para la implementación de prótesis auditivas encaminadas a compensar adecuadamente las pérdidas neurosensoriales al tratarse de un procesado no lineal que aplica una función de compensación dependiente de los parámetros del propio paciente. Se trata, por lo tanto, de una prótesis específica para cada paciente, ya que, tal y como se ha indicado anteriormente, utiliza unos medios de almacenamiento como preferentemente una memoria RAM, una memoria RAM estática, una memoria EPROM o similares, para almacenar los datos por frecuencia que se emplean en la modificación de la amplitud. Asimismo, el procesador anteriormente descrito cumple las características de pequeño tamaño y bajo consumo, al optar por la realización de una FFT de mediano tamaño (64 puntos por marco), reduciéndose el almacenamiento de datos gracias a la implementación de un algoritmo modificado de geometría constante “*in-place*” para la FFT y su inversa. Finalmente, para disminuir la introducción de ruido debido a las operaciones aritméticas, se ha optado por extender la longitud de las palabras a utilizar en lugar de usar operaciones en punto flotante.

Para comprender mejor el objeto de la presente invención se describe a continuación una realización práctica preferencial del procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes, así como del procesador digital para la realización de dicho procedimiento, en base a las figuras adjuntas. En dichas

figuras se muestra:

La figura 1 muestra un diagrama de flujo del procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes objeto de la presente invención.

La figura 2 muestra un diagrama de bloques del circuito de una realización preferente del procesador digital para la realización del procedimiento representado en la figura anterior.

Tal y como se representa en la figura 1, el procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes objeto de la presente invención comienza por la recepción (1) de la señal en el tiempo de entrada  $x(t)$  en bloques de 64 puntos. Sobre cada uno de dichos bloques de 64 puntos de la señal de entrada  $x(t)$  se realiza la Transformada Rápida de Fourier (RFFT) (2), para obtener la representación espectral de cada uno de dichos bloques de señal.

A continuación se realiza la representación exponencial (3) de las componentes en frecuencia obtenidas en dicha representación espectral:

$$S_K = A_K e^{j\theta_K} \quad (1.2)$$

donde  $A_K$  representa la amplitud y  $\theta_K$  representa la fase.

Para obtener una nueva señal auditiva con los componentes de frecuencia dentro del rango dinámico del paciente con pérdidas, se utilizan todos los armónicos disponibles ( $S_K$ ), modificando el parámetro de amplitud por medio de una función de compensación acústica (4) dada por:

$$\frac{\alpha^i_K - Pn}{Dn - \alpha^i_K} = \frac{\alpha^o_K - Pp}{Dp - \alpha^o_K} \quad (2.2)$$

donde  $\alpha^i_K$  y  $\alpha^o_K$  representan la amplitud en decibelios de los armónicos ( $A^i_K$ ) y ( $A^o_K$ ), a modificar respectivamente,  $Pn$  y  $Dn$  los niveles de percepción y dolor para un oyente normal,  $Pp$  y  $Dp$  los niveles de percepción y dolor para un oyente con pérdidas.

De la ecuación anterior (2.2) se obtiene una función con la amplitud modificada dada por:

$$A^o_K = K_1 (A^i_K)^{K_2} \quad (3.2)$$

manteniendo la fase original, y donde  $K_1$  y  $K_2$  son constantes derivadas de los niveles de percepción y dolor del individuo.

Una vez modificada la amplitud de los armónicos se obtiene el nuevo componente en frecuencia que mantiene la fase original (5).

Esta nueva señal es sintetizada por medio de la Transformada Inversa Rápida de Fourier (IFFT) (6), proporcionando (7) la señal de salida en el dominio del tiempo  $y(t)$ .

Además de las operaciones ya indicadas, dicho procedimiento comprende de un sencillo control de ruido que permite la eliminación de sonidos molestos en determinados ambientes.

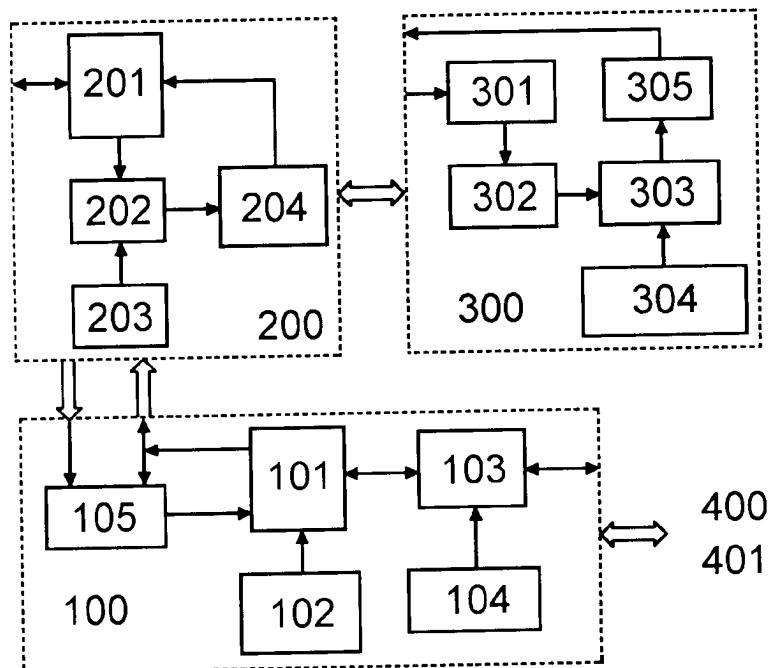

Las figuras 2 muestra un diagrama de bloques detallado del procesador digital para la realización del procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes anteriormente descrito. Tal y como se representa en

dicha figura 2, el circuito del procesador digital ha sido dividido para su diseño en tres módulos funcionales, como son un bloque de entrada/salida (100), que se encarga de introducir los datos desde el conversor así como de dar salida a los que ya han sido modificados, un bloque de FFT (200) que realiza la Transformada Rápida de Fourier directa e inversa sobre los datos introducidos, y un bloque de modificación de armónicos (300), que aplica la compresión a los armónicos obtenidos tras la Transformada de Fourier directa. A continuación se describirán las características principales de cada uno de dichos bloques, así como los bloques que los componen.

Tal y como se ha indicado anteriormente, el bloque de entrada/salida (100) es el bloque encargado de introducir los datos desde el conversor así como de dar salida a los que ya han sido modificados. El módulo principal de este bloque lo forma la cola de entrada/salida, compuesta por una memoria RAM (101) con dos puertos completamente independientes de lectura/escritura, con una capacidad de 64 palabras de 14 bits (resolución del conversor) que, junto con unos contadores (102) de datos almacenados, hace las veces de una cola FIFO de datos.

Un puerto y su contador es utilizado exclusivamente por los Registros Serie  $\leftrightarrow$  Paralelo para leer los datos ya modificados y enviarlos al conversor digital a analógico (conversor D/A) (400), y para escribir los datos nuevos muestreados por el conversor analógico a digital (conversor A/D) (401), intercambiándose ambos datos en la posición que indique el contador en ese momento. Este contador tomará valores de 0 a 63 y avanza según se lee y escribe cada dato, por lo que se van escribiendo los datos ordenadamente en la memoria (101) y de manera circular.

El otro puerto con su contador se utiliza para realizar el intercambio de datos con el bloque de la FFT (200), leyendo y escribiendo datos durante la denominada etapa de carga, en la cual los datos ya modificados que residen en la memoria de trabajo (201) se vuelcan a la FIFO de entrada/salida (101), y los datos nuevos que se van obteniendo en esta última se escriben en dicha memoria de trabajo (201). Este intercambio de datos entre la FIFO de entrada/salida (101) y la memoria de trabajo (201) se realiza de uno en uno.

Para cada transformada se utiliza un solapeamiento de 16 datos. Es decir, si los anteriores 64 datos fueron:

*Marco N-1: X<sub>0</sub>, ..., X<sub>48</sub>, X<sub>49</sub>, ..., X<sub>63</sub>*

cuando lleguen los siguientes 48 datos nuevos, el marco actual de 64 datos quedará como:

*Marco N: X<sub>48</sub>, ..., X<sub>63</sub>, Y<sub>64</sub>, ..., Y<sub>111</sub>.*

Sin embargo, los datos no están dispuestos en memoria de esta manera, sino que siempre se encuentran en la primera posición de la FIFO de entradasalida (101) los 48 datos nuevos y a continuación los 16 antiguos, por lo que se ha diseñado un contador cíclico módulo 64 que avanza 48 posiciones cada vez que comenzamos el volcado de datos a memoria, y empieza a leer a partir de la siguiente de uno en uno. Así conseguimos obtener

primero los 16 datos anteriores y a continuación los 48 nuevos.

Otro módulo destacado del bloque de entrada/salida (100) lo constituyen los circuitos de comunicación con el conversor (103), que constan de dos registros de desplazamiento. El primero de ellos se encarga de la adquisición de datos serie provenientes del conversor A/D (401) y de la posterior entrega de éstos en formato paralelo a la FIFO de entrada/salida (101). El segundo de dichos registros de desplazamiento realiza la función opuesta, es decir, recibe un dato de salida proveniente de la FIFO de entrada/salida (101) y lo envía en serie hacia el conversor D/A (400). Dicho bloque de circuitos de comunicación con el conversor (103) se encarga también de producir una señal de fin de comunicación para indicar que el dato de entrada es estable y que se puede volcar un nuevo dato de salida.

Asimismo, en dicho bloque de entrada/salida (100) se dispone un bloque de programación del conversor (104) que se encarga de fijar el valor de los registros responsables de cambiar la frecuencia de muestreo de la señal analógica a las necesidades concretas. Esta programación se produce antes del funcionamiento normal del circuito.

Finalmente, en el bloque de entrada/salida (100) se implementa un control de ruido (105) que se encarga de realizar la media de los 64 valores que forman un marco. Dicho resultado se compara con los valores de histéresis programados desde el exterior. Si el valor de la media es mayor que la cota superior, el marco completo es escrito en la FIFO de entrada/salida (101) para su posterior conversión; pero si por el contrario, la media es menor que el valor inferior de la histéresis, los valores que se escriben en la FIFO de entrada/salida (101) para este marco son ceros. En el caso de que la media esté comprendida entre las cotas superior e inferior, la salida dependerá del valor de la media del marco anterior, es decir, sólo saldrá el marco tratado si lo hizo el anterior. El resultado de este tratamiento sólo afectará a la salida si se tiene la señal externa de control de ruido activada. En caso contrario, el marco de datos que se escribe será el que proviene del bloque de la FFT (200).

Un segundo bloque de dicho procesador digital para la realización del procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes representado en la figura 2 lo constituye el bloque FFT (200), que se encarga de calcular la transformada rápida de Fourier directa e inversa. Dicho bloque comprende cuatro módulos principales, más la lógica de control. El primero de estos módulos está formado por una RAM de doble puerto (16 x 64) (201), utilizada para almacenar los datos sobre los que trabajamos mientras se están realizando las transformadas de Fourier directa e inversa, así como la modificación de los armónicos. Los datos que se leen de la memoria de trabajo se distribuyen a tres lugares, dependiendo de la fase de operación en la que se esté: módulo de cálculo o mariposa (202), bloque de entrada/salida (100) y bloque de modificación de armónicos (300).

El ancho de cada dato es de 16 bits, en lugar de

los 14 bits que poseen las palabras que provienen del conversor. Esto es debido a que se introducen dos bits adicionales que extenderán la longitud de palabra para mejorar precisión de los cálculos que se efectúan con aritmética entera.

Dicha memoria tiene una disposición especial, puesto que en lugar de utilizar 64 posiciones, se ha optado por crear una memoria con tan solo 16 posiciones, y en cada una de ellas se almacenan los cuatro datos que se van a utilizar para el cálculo de una mariposa en la FFT, donde, a partir de ahora, designamos como mariposa de una FFT a las operaciones aritméticas que se realizan sobre conjuntos de r-datos, todos ellos necesarios en los cálculos, en cada una de las etapas de una FFT de radix r. Cada mariposa acepta r datos de entrada y produce r datos de salida. Esto tiene una ventaja importante, ya que tan sólo habrá que realizar una lectura para obtener los cuatro datos con los que operamos, y sólo una escritura para almacenarlos, por lo que se reduce el número total de operaciones de lectura/escritura.

Para ello se tienen que disponer los datos en la memoria de una forma especial así como utilizar un direccionamiento muy concreto. La forma de actuar normal será operar con el primer grupo de datos y a continuación con la siguiente mariposa que posea el mismo tipo de rotación que la anterior, guardando dos datos de cada mariposa en la posición que dejó libre la primera, y seguidamente todos los datos restantes en la posición que ocupaba la segunda. De esta forma se opera en todas las etapas, comenzando por las mariposas reales y a continuación las complejas, aumentando progresivamente el ángulo de la rotación y recordando siempre que se guardan juntos los datos que proporcionan dos mariposas realizadas consecutivamente y que poseen el mismo ángulo de rotación. En algunas etapas (como la primera y la última de la FFT directa) el almacenamiento se realizará de forma diferente, guardando los cuatro resultados de una mariposa en la misma posición de la que provienen, consiguiendo de esta manera dejar dispuestos los datos correctamente para realizar la FFT inversa.

De esta forma no sólo se consigue que el algoritmo de la FFT sea "in-place", sino que además reduce a la cuarta parte el número de ciclos de lectura y escritura. Entendiendo por algoritmo in-place referido a una FFT un algoritmo que escriba los datos resultantes de una mariposa en la misma posición de memoria que los datos que han sido utilizados para el cálculo de ésta y que por lo tanto no necesita una cantidad de memoria adicional.

Las principales operaciones aritméticas que se llevan a cabo sobre los datos en las transformadas directa e inversa son realizadas por el módulo mariposa (202), y que posee la mayor parte de los bloques de cálculo, como son dos sumadores, dos restadores, un multiplicador 16 x 16, un sumador/restador, dos complementadores a 2 y lógica de control.

La mariposa (202) obtiene los cuatro datos de la memoria de trabajo (201) y opera sobre ellos, de forma que es capaz de realizar dos mariposas reales simultáneamente o bien una mariposa con datos complejos. Para poder realizar las maripo-

sas complejas se necesitan los senos y cosenos de ciertos ángulos constantes, en el presente caso de 16 ángulos, los cuales se proporcionan desde un módulo de generación de senos y cosenos (203). En dicho módulo de generación de senos y cosenos (203) se ha reducido a la mitad el número de valores almacenados debido a que la otra mitad se obtiene por simetría, es decir, complementando a 2 y/o intercambiando los valores de los senos y cosenos. Estos datos se suelen almacenar en una memoria ROM 16 x 16 (ocho senos y ocho cosenos), o bien cablearse directamente con lógica combinacional, con el objeto de reducir el retraso de lectura, el consumo de potencia así como el área ocupado.

Una vez concluido el cálculo de una mariposa, se lleva a cabo una reorganización de datos en una FIFO de ordenación de datos (204), dispuesta a la salida de la mariposa (202) con el objeto de reordenar los datos correctamente para ser escritos en la memoria de trabajo (201), de forma que los cuatro datos que se necesitan en la próxima etapa estén almacenados en la misma, posición de memoria. Dicha FIFO de ordenación de datos (204) del bloque FFT (200) está compuesta por dos colas de diferente longitud (de una y dos posiciones), de forma que los dos datos superiores de la mariposa entran en la FIFO-1 y los dos inferiores en la FIFO-2, escogiéndose finalmente a la hora de escribir los datos, la cola que interese.

El bloque de modificación de armónicos (300) se encarga de comprimir los armónicos una vez realizada la transformada de Fourier directa. Esta compresión consiste básicamente en tomar la componente real e imaginaria de cada armónico, calcular su módulo, convertirlo a escala logarítmica, multiplicarlo por un factor de compresión comprendido entre 0 y 1, sumarle una constante y volver a expresarlo en forma lineal. El resultado así obtenido se multiplica por las componentes real e imaginaria del armónico para obtener los valores definitivos. Tanto el factor de compresión como la constante dependerán de la frecuencia del armónico que se esté tratando.

Por lo tanto, dicho bloque de modificación de armónicos comprende un bloque de cálculo de módulo (301), utilizando una aproximación al valor exacto mediante un método de rotaciones, ya que el cálculo de la raíz cuadrada sería muy costoso. Asimismo se dispone un bloque de conversión a decibelios (302) apto para convertir el valor de la escala lineal a decibélica.

La compresión del armónico se realiza en el bloque de compresión del armónico (303), obteniéndose tanto el factor de compresión como la constante a sumar de una memoria RAM de datos del paciente (304), siendo cada uno de dichos factores de ocho bits, estando almacenados en una sola palabra de 16 bits para obtenerse mediante una única lectura en memoria. Dichos medios de almacenamiento constituidos en el presente ejemplo de realización práctica por una memoria RAM (304) se pondrán implementar igualmente mediante una memoria RAM estática, una memoria EPROM u otras similares.

Finalmente, se dispone también de un circuito de conversión de decibelios a valores lineales (305).

La conversión de escala lineal a decibelios y viceversa se realiza utilizando un algoritmo de aproximación del logaritmo mediante el uso de potencias de dos. Más concretamente, la conversión de escala lineal a decibelios comprende el cálculo para el valor del módulo a tratar de la potencia de dos inferior más próxima, la construcción de la parte entera de un número constituido por dicha potencia de dos inferior más próxima mas unos cuantos bits decimales procedentes del módulo, para mejorar la precisión de este valor, y multiplicar el número así obtenido por  $20 \log_2$  ( $\cong 6.020599913$  dB), obteniendo el valor en decibelios (dB).

Asimismo, la operación inversa, esto es, la conversión de decibelios a valores lineales comprende la división del valor por  $20 \log_2$  ( $\cong 6.020599913$

*dB*), obteniendo un exponente con el que se calcula la potencia de dos que da el factor definitivo, calculándose la potencia de 2 con la parte entera del exponente, uniéndose al número obtenido los decimales del propio exponente, multiplicándose el factor obtenido por cada una de las componentes real e imaginaria del armónico tratado para obtener en forma binomial el valor definitivo.

Una vez descrita suficientemente la naturaleza de la presente invención, así como una forma de llevarla a la práctica, sólo nos queda por añadir que en su conjunto y partes que lo componen es posible introducir cambios de forma, materiales y de disposición, siempre y cuando dichas alteraciones no varíen sustancialmente las características de la invención que se reivindican a continuación.

5

10

15

20

25

30

35

40

45

50

55

60

65

## REIVINDICACIONES

1. Procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes, del tipo de los que se utilizan para compensar la señal hablada a personas con pérdidas neurosensoriales con el objeto de aumentar su inteligibilidad, **caracterizado** porque comprende:

- la recepción (1) de la señal en el tiempo  $x(t)$  de entrada en bloques de 64 puntos;

- la obtención de la representación espectral de cada uno de dichos bloques de señal en el tiempo mediante la Transformada Rápida de Fourier (FFT) (2);

- la representación exponencial (3) de las componentes en frecuencia obtenidas en dicha representación espectral

$$S_K = A_K e^{j\theta_K}$$

donde  $A_K$  representa la amplitud y  $\theta_K$  representa la fase;

- la aplicación de una función de compensación acústica aplicada sobre la amplitud de cada uno de los armónicos obtenidos en dicha representación, exponencial, obtenida a partir de la relación:

$$\frac{\alpha^i_K - P_n}{D_n - \alpha^i_K} = \frac{\alpha^o_K - P_p}{D_p - \alpha^o_K} \quad (2.1)$$

representando  $\alpha^i_K$  y  $\alpha^o_K$  la amplitud en decibelios de los armónicos ( $A^i_K$ ) y ( $A^o_K$ ), a modificar respectivamente,  $P_n$  y  $D_n$  los niveles de percepción y dolor para un oyente normal,  $P_p$  y  $D_p$  los niveles de percepción y dolor para un oyente con pérdidas, obteniendo unos nuevos armónicos modificados en amplitud dados por:

$$A^o_K = K_1 (A^i_K)^{K_2} \quad (3.1)$$

manteniendo la fase original, y donde  $K_1$  y  $K_2$  son constantes derivadas de los niveles de percepción y dolor del individuo; y

- la sintetización de dicha señal espectral modificada mediante (5) la Transformada Inversa Rápida de Fourier (IFFT) (6), para obtener la señal en el tiempo de salida  $y(t)$ .

2. Procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes, acorde con la primera reivindicación, **caracterizado** porque comprende preferentemente un sencillo control de ruido apto para la eliminación de sonidos molestos en determinados ambientes.

3. Procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes, acorde con la primera reivindicación, **caracterizado** porque el cálculo de las transformadas de Fourier directa e inversa utiliza un algoritmo modificado de geometría constante “in-place” implementado a través de una memoria RAM de doble puerto y capacidad para cuatro datos en cada palabra, que comprende la operación con el primer grupo de datos y a continuación con la siguiente mariposa que posea el mismo tipo de rotación que

5

10

15

20

25

30

35

40

45

50

55

60

65

la anterior, guardando dos datos de cada mariposa en la posición que dejó libre la primera, y seguidamente todos los datos restantes en la posición que ocupaba la segunda, comenzando en todas las etapas de cálculo por las mariposas reales y a continuación las complejas, aumentando progresivamente el ángulo de la rotación y guardando juntos los datos que proporcionan dos mariposas realizadas consecutivamente y que poseen el mismo ángulo de rotación.

4. Procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes, acorde con la reivindicación 3, **caracterizado** porque en algunas etapas (como la primera y la última de la FFT directa) el almacenamiento se realizará de forma diferente, guardando los cuatro resultados de una mariposa en la misma posición de la que provienen.

5. Procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes, acorde con las reivindicaciones 3 y 4, **caracterizado** porque una vez concluido el cálculo de una mariposa, se lleva a cabo una reorganización de datos apta para reordenar los datos correctamente para ser escritos en la memoria de trabajo, de forma que los cuatro datos que se necesitan en la próxima etapa estén almacenados en la misma posición de memoria.

6. Procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes, acorde con las reivindicaciones 1 a 5, **caracterizado** porque dicha fase de aplicación de una función de compensación acústica (4) comprende operaciones de conversión de escala lineal a decibelios basadas en un algoritmo de aproximación mediante el uso de potencias de dos, que comprende el cálculo para el valor del módulo a tratar de la potencia de dos inferior más próxima, la construcción de la parte entera de un número constituido por dicha potencia de dos inferior más próxima mas unos cuantos bits decimales procedentes del módulo, para mejorar la precisión de este valor, y multiplicar el número así obtenido por  $20\log_2$  ( $\cong 6.020599913$  dB), obteniendo el valor en decibelios (dB).

7. Procedimiento para el tratamiento de señales de audio descompuestas en 32 bandas de frecuencia con compresión de amplitudes, acorde con las reivindicaciones 1 a 5, **caracterizado** porque dicha fase de aplicación de una función de compensación acústica (4) comprende operaciones de conversión de decibelios a valores lineales basadas en un algoritmo de aproximación mediante el uso de potencias de dos, que comprende la división del valor por  $20\log_2$  ( $\cong 6.020599913$  dB), obteniendo un exponente con el que se calcula la potencia de dos que da el factor definitivo, calculándose la potencia de 2 con la parte entera del exponente, uniéndose al número obtenido los decimales del propio exponente, multiplicándose el factor obtenido por cada una de las componentes real e imaginaria del armónico tratado para obtener en forma binomial el valor definitivo.

8. Procesador digital para la implementación del procedimiento acorde con las reivindicaciones

anteriores, a utilizar preferentemente en la industria dedicada a la fabricación de prótesis auditivas digitales de ayuda a individuos con pérdidas acústicas, **caracterizado** porque comprende los siguientes módulos funcionales:

- un bloque de entrada/salida (100), apto para introducir los datos desde un conversor analógico a digital (conversor A/D) (401) de entrada y para entregar en su salida los datos tratados a un conversor digital a analógico (conversor D/A) (400);

- un bloque que realiza la transformada rápida de Fourier, denominado de aquí en adelante *bloque FFT* (200), apto para realizar la transformada rápida de Fourier directa e inversa sobre los datos introducidos a través de dicho bloque de entrada/salida (100); y

- un bloque de modificación de armónicos (300), apto para realizar una operación de compresión sobre los armónicos obtenidos una vez realizada la transformada directa de Fourier sobre los datos introducidos mediante dicho bloque FFT (200).

9. Procesador digital acorde con la reivindicación 8, **caracterizado** porque el bloque de entrada/salida (100) comprende:

- una cola de entrada/salida, preferentemente una cola FIFO de datos, constituida por una memoria RAM (101), apta para almacenar los datos de entrada hasta completar un marco a tratar así como para suministrar al exterior los resultados modificados, con dos puertos de lectura/escritura completamente independientes, y un conjunto de contadores (102);

- circuitos de comunicación con el conversor (103), que constan preferentemente de dos registros de desplazamiento, aptos para, respectivamente, la conversión serie-paralelo de los datos serie provenientes del conversor A/D (400) para su posterior entrega a dicha cola de entrada/salida, y para la conversión paralelo-serie de los datos paralelo provenientes de dicha cola de entrada/salida al conversor D/A (401), y apto para producir una señal de fin de comunicación para indicar que el dato de entrada está estable y se puede volcar un nuevo dato de salida;

- un bloque de programación del conversor (104), apto para fijar el valor de los registros responsables de cambiar la frecuencia de muestreo de la señal analógica; y

- un control de ruido (105), apto para realizar la media de los valores que forman un marco FFT.

10. Procesador digital acorde con la reivindicación 9, **caracterizado** porque dicha memoria RAM (101) de dicho bloque de entrada/salida (100) presenta una dimensión de preferentemente 64 x 14, para almacenar 64 palabras de 14 bits.

11. Procesador digital acorde con la reivindicación 9, **caracterizado** porque la programación

de dicho bloque de programación del conversor (105) se realiza preferentemente antes de la puesta en marcha del circuito.

5 12. Procesador digital acorde con la reivindicación 8, **caracterizado** porque dicho bloque FFT (200) comprende:

- una memoria RAM de doble puerto (201), apta para almacenar los datos sobre los que se trabaja mientras se están realizando las transformadas de Fourier directa e inversa, así como la modificación de los armónicos;

- un módulo de cálculo o *módulo mariposa* (202) que comprende la mayor parte de bloques de cálculo como son dos sumadores, dos restadores, un multiplicador, un sumador/restador, dos complementadores a 2 y lógica de control;

-un módulo de generación de senos y cosenos (203);

- una cola FIFO de ordenación de datos (204), apta para reorganizar los datos de salida de dicho módulo mariposa (202) para su escritura en dicha memoria RAM (201); y

- lógica de control.

20 13. Procesador digital acorde con la reivindicación 12, **caracterizado** porque la dimensión de dicha memoria RAM de doble puerto (201) es preferentemente de 16 x 64.

25 14. Procesador digital acorde con la reivindicación 12, **caracterizado** porque dicha FIFO de ordenación de datos (204) del bloque FFT (200) está compuesta por dos colas de diferente longitud (de una y dos posiciones), con conexiones aptas para introducir los dos datos superiores de la mariposa en la FIFO-1 e introducir los dos datos inferiores en la FIFO-2.

30 15. Procesador digital acorde con la reivindicación 8, **caracterizado** porque dicho bloque de modificación de armónicos (300) comprende:

- un módulo de cálculo del módulo (301) del armónico correspondiente;

- un módulo de conversión de escala lineal a escala logarítmica (302);

- medios de almacenamiento aptos para almacenar los datos particulares del paciente, constituidos preferentemente por una memoria RAM (304), una memoria RAM estática, una memoria EPROM o similares;

- medios para aplicar la compresión del armónico (303), consistente preferentemente en la multiplicación del módulo del armónico en escala logarítmica por un factor de compresión comprendido entre cero y uno y la suma de una constante, dependiendo tanto el factor de compresión como la constante de la frecuencia del armónico que se está tratando; y

- un módulo de conversión de escala logarítmica a escala lineal (305).

Fig. 1

Fig. 2

OFICINA ESPAÑOLA

DE PATENTES Y MARCAS

ESPAÑA

- (11) ES 2 130 997

(21) N.º solicitud: 9701080

(22) Fecha de presentación de la solicitud: 20.05.97

(32) Fecha de prioridad:

## INFORME SOBRE EL ESTADO DE LA TECNICA

(51) Int. Cl.<sup>6</sup>: H04R 25/00

### DOCUMENTOS RELEVANTES

| Categoría | Documentos citados                                                                              | Reivindicaciones afectadas |

|-----------|-------------------------------------------------------------------------------------------------|----------------------------|

| A         | US 5388185 A (TERRY et al.) 07.02.1995, columna 3, línea 36 - columna 8, línea 25; figuras 1-5. | 1                          |

| A         | US 5355418 A (KELSEY et al.) 11.10.1994, todo el documento.                                     | 1                          |

| A         | US 5029217 A (CHABRIES et al.) 02.07.1991, columna 4, línea 50 - columna 15, línea 21; figuras. | 1,2                        |

| A         | US 5274711 A (RUTLEDGE et al.) 28.11.1993, columna 3, línea 15 - columna 9, línea 2; figuras.   | 1,8                        |

#### Categoría de los documentos citados

X: de particular relevancia

O: referido a divulgación no escrita

Y: de particular relevancia combinado con otro/s de la misma categoría

P: publicado entre la fecha de prioridad y la de presentación de la solicitud

A: refleja el estado de la técnica

E: documento anterior, pero publicado después de la fecha de presentación de la solicitud

#### El presente informe ha sido realizado

para todas las reivindicaciones

para las reivindicaciones nº:

|                                              |                                 |               |

|----------------------------------------------|---------------------------------|---------------|

| Fecha de realización del informe<br>18.05.99 | Examinador<br>M. Alvarez Moreno | Página<br>1/1 |

|----------------------------------------------|---------------------------------|---------------|