REGISTRO DE LA

PROPIEDAD INDUSTRIAL

ESPAÑA

(11) N.º de publicación: ES 2 010 398

(21) Número de solicitud: 8900442

(51) Int. Cl.<sup>4</sup>: G01T 1/17

12

## PATENTE DE INVENCION

A6

22) Fecha de presentación: **08.02.89**

⑦ Titular/es: **Centro de Investigaciones Energéticas, Medioambientales y Tecnológicas. (C.I.E.M.A.T.)**

**Avda. Complutense, 22**

**Madrid, ES**

④(5) Fecha de anuncio de la concesión: **01.11.89**

72 Inventor/es: **García Belmonte, Germán;

Olmos Moreno, Pedro y

Pérez Morales, José Manuel**

④(5) Fecha de publicación del folleto de patente:

**01.11.89**

74) Agente: **García Cabrerizo, Francisco**

54) Título: Método discriminador de señal electrónica basado en un circuito promediador.

## 57 Resumen

Resumen

Método discriminador de señal electrónica basado en un circuito promediador, mediante el cual es posible detectar señales electrónicas en presencia de un ruido aleatorio elevado, con baja relación señal-ruido. El sistema se basa en un filtrado digital recursivo de tipo promediador, y  $(k) = y(k+1) + x(k)$ , y está implementado en un circuito electrónico que usando la entrada analógica, es capaz de suministrar una salida digital cuando está presente un comportamiento no aleatorio. Este método es especialmente útil, asociado con detectores nucleares de semiconductos trabajando a temperaturas ambiente, en donde los detectores son altamente ruidosos.

## DESCRIPCION

La presente invención se refiere a un procedimiento de discriminación de señal. Puede ser usado en aplicaciones en las que el ruido de banda ancha supere la amplitud de la señal. El método resulta especialmente útil para sistemas con SNR inferior a la unidad, donde la señal presente una pendiente de subida relativamente lenta ( $\sim 1\mu\text{s}$ ). La discriminación se realiza mediante un filtrado digital de tipo sumador, siguiendo una ley:  $y(k) = x(k) + y(k-1)$

El método tiene especial aplicabilidad en la discriminación de la señal producida por un detector nuclear altamente ruidoso.

Es sabido que los métodos tradicionales de tratamiento de señal para detectores nucleares, basados en el esquema preamplificador-discriminador-formador de impulso, resultan inadecuados si se quieren emplear con materiales semiconductores de elevada densidad. Estos materiales se caracterizan por una elevada energía de "gap" y por un valor pobre del producto  $\mu\tau$ . Así, los pulsos de corriente generados en el material son extremadamente pequeños. Es decir, se obtienen valores pobres en la relación S/N (señal ruido) y por tanto, bajos niveles de confianza en la determinación de presencia de impulso, cuando ésta se realiza por simple discriminación sobre un umbral prefijado. Como consecuencia de ello, aumenta el error existente en este tipo de sistemas de conteo.

En el método que nos ocupa la discriminación se efectúa mediante una estructura de tipo recursivo, a altas velocidades de muestreo. Un procedimiento del tipo:

$$y(k) = x(k) + y(k-1)$$

resuelve el problema de una manera sencilla. Se garantiza la estabilidad del sistema cuando las muestras  $x(k)$ , están distribuidas de manera aleatoria alrededor del valor cero. Por el contrario, si las muestras presentan alguna correlación, el sistema deja de ser estable y responde con una evolución muy rápida, incluso si la entrada  $x(k)$ , está inmersa en el nivel de ruido.

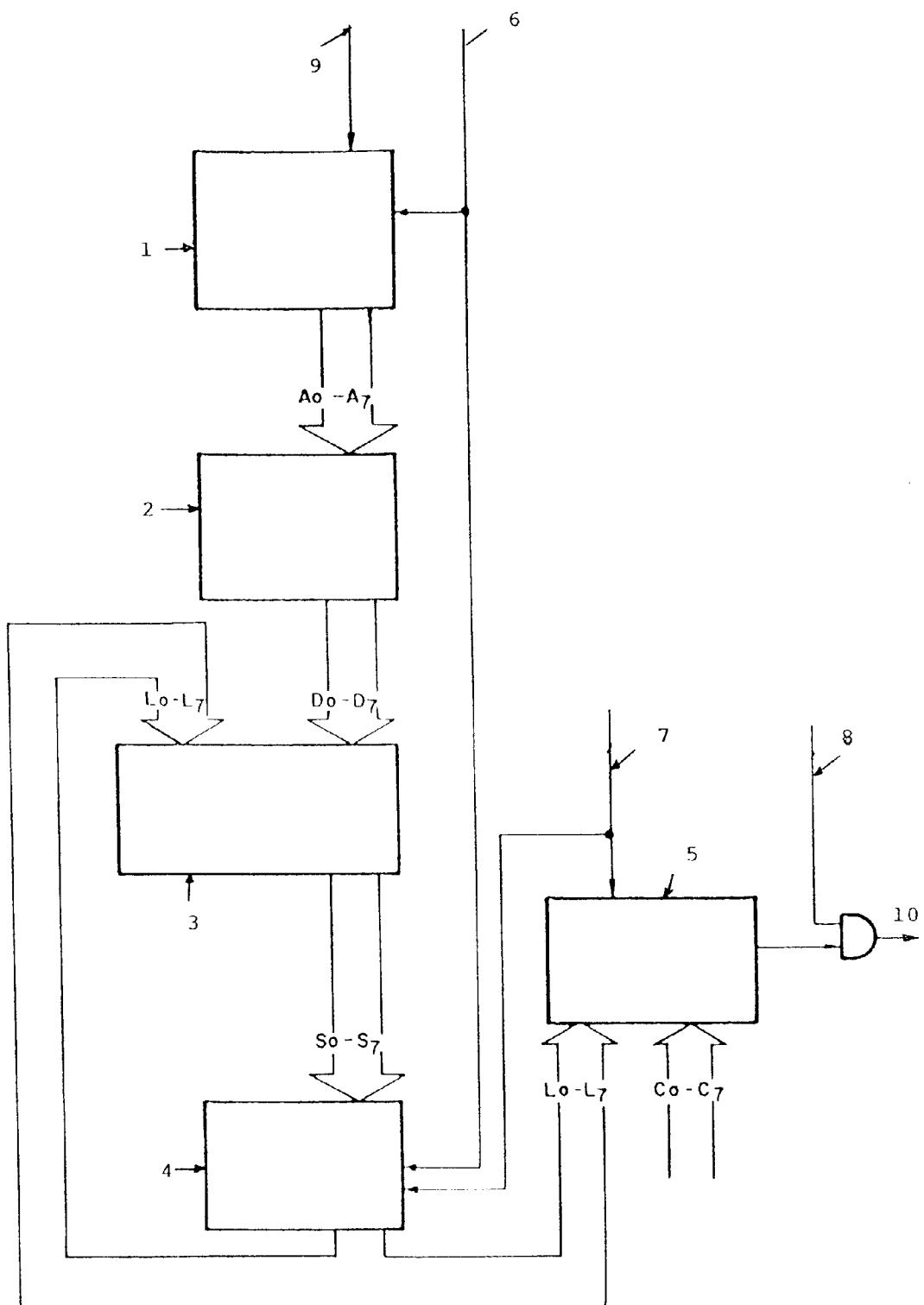

Una implementación del método descrito, se representa en el diagrama de bloques que se adjunta, en el que se han representado los diferentes bloques electrónicos que componen el circuito para la realización del método referido.

La descripción que sigue se hace en relación con dicha Figura, presentando una forma de realización general del método.

La señal que se desea discriminar llega a un conversor analógico-digital (1) de alta velocidad, el cual codifica la señal de entrada entre una refe-

rencia inferior y otra superior. La orden de conversión viene dada por la rampa de subida de un oscilador maestro, CLK. (6).

La señal de entrada al circuito conversor-analógico -digital (1) puede tener componentes tanto positivas como negativas. Las primeras corresponden a señales de tensión de ruido negativo y las segundas a los correspondientes ruidos positivos más la señal. Es por esto que se reorganiza el rango del conversor-analógico -digital (cero-rango máximo positivo) dando lugar a (rango máximo negativo-cero-rango máximo positivo). De esto se encarga el circuito inversor de bits (2). Así, podemos variar el nivel de situación del nuevo "cero" en la escala originaria del conversor-analógico-digital. (1).

Así ordenados los bits, entran en un circuito sumador (3) que procede a sumar este valor con el que tiene cargado en un registro "latch" (4). Realizada la operación se carga el "latch" con el valor resultante. Se ha de asegurar la estabilidad de las entradas del sumador durante la adición, para ello la señal CLK (6), de conversión del convertidor-analógico-digital (1) gobierna también el registro "latch".

Por último, se dispone un circuito comparador (5) que tiene por objeto establecer si la salida del promediador supera un cierto umbral, en cuyo caso se dispara la salida. También se incluye una línea RESET (7) que pone a cero todos los elementos del sistema, permitiendo el inicio de otro ciclo de promediado. Además, se debe implementar una línea INHIBIT (8) que mantiene la salida a cero, con el fin de disponer de un conjunto estadísticamente significativo de muestras.

Las conexiones entre las diferentes partes de que consta el sistema puede apreciarse en el diagrama de bloques de la Figura.

Así, la señal analógica externa INPUT (9) ataca el circuito-analogico-digital (1), que es gobernado por la señal de reloj CLK (6). La salida del circuito-analógico -digital (1) (AO-A<sub>7</sub>) entra en el inversor de bits (2), el cual da como salida (DO-D<sub>7</sub>). Esta señal (DO-D<sub>7</sub>) y la salida del "latch" (4) (LO-L<sub>7</sub>) atacan el sumador (3) dando como salida (SO-S<sub>7</sub>) que entra en el "latch" (4) gobernado por la misma señal externa CLK (6). La salida del "latch" (4) LO-L<sub>7</sub> es comparada en el circuito comparador (5) con un nivel externo de comparación CO-C7. La salida del comparador es 1 si LO-L<sub>7</sub> supera CO-C7 y 0 en caso contrario. Esta salida y la señal externa INHIBIT (8) atacan una puerta lógica AND y de aquí se obtiene la salida OUT (10). La línea RESET (7) convierte en cero el valor acumulado en el "latch" y el comparador.

## REIVINDICACIONES

1. Método discriminador de señal electrónica basado en un circuito promediador, que siendo de especial aplicabilidad en la discriminación de la señal producida por un detector nuclear altamente ruidoso, con el fin de poder detectar señales electrónicas en presencia de un ruido aleatorio elevado, con baja relación señal/ruido; se **caracteriza** esencialmente porque consiste en realizar un filtrado digital recursivo de tipo sumador, de acuerdo con la Ley de muestreo  $y(k) = x(k) + y(k-1)$ , efectuándose la discriminación a altas velocidades de muestreo.

2. Método discriminador de señal electrónica basado en un circuito promediador, de acuerdo con la reivindicación 1<sup>a</sup>, **caracterizado** porque el circuito promediador propiamente dicho, para la realización del método discriminador, incluye en primer término un convertidor-analógico-digital (1) al que accede la correspondiente

señal analógica externa (9) a tratar, señal que es codificada y pasa a un circuito inversor de bits (2), siendo tales bits a un sumador (3), a continuación del cual se ha previsto un registro “latch” (4); siendo la señal de salida de dicho “latch” (4) enviada a un comparador (5), cuya finalidad es la de establecer si la salida del circuito supera un cierto umbral; habiéndose previsto que el convertidor-analógico-digital (1) sea gobernado por una señal de reloj CLK (6), la cual gobierna asimismo el “latch” (4).

3. Método discriminador de señal electrónica basado en un circuito promediador, de acuerdo con la reivindicación 2<sup>a</sup>, **caracterizado** porque la señal de salida externa (8) del comparador (5) es enviada hacia una puerta lógica AND de la que se obtiene la salida OUT (10); habiéndose previsto una señal RESET (7) para poner a cero los valores acumulados tanto en el “latch” (4), como en el comparador (5).

25

30

35

40

45

50

55

60

65

FIG. 1